KNOW INTUIT, Лекция, Основи на превключването

Архитектура на превключвателя

Един от основните компоненти на цялото комутационно оборудване епревключвателната тъкан. Превключващата матрица е чипсет, който свързва множество входове с множество изходи въз основа на фундаментални комутационни технологии и принципи. Превключващата матрица изпълнява три функции:

- превключва трафика от един матричен порт към друг, като гарантира тяхната еквивалентност;

- осигурява качество на услугата (Quality of Service, QoS);

- осигурява толерантност към грешки.

Тъй като превключващата тъкан е ядрото на хардуерната платформа, тя подлежи на изисквания за мащабиране на производителността и способността за бързо развитие на QoS системата.

„Неблокираща“ превключваща тъкан(неблокираща превключваща тъкан)е тъкан, в която производителността и QoS не зависят от типа трафик, превключван през тъканта, и производителността е равна на сбора от скоростите на всички портове:

където 1 Умножение по 2 за дуплексен режим е броят на портовете, е максималната пропускателна способност на протокола, поддържан от i-тия порт на комутатора.

Например производителността на суич с 24 10/100 Mbps порта и 2 1 Gbps порта се изчислява, както следва:

Превключвателят предоставя на портовете равен достъп до тъканта, ако системата не задава приоритет на някои портове пред други.

Тъй като комутационната тъкан е разположена в основата на комутационната платформа, един от най-важните въпроси остава нейната устойчивост на грешки. Този проблем се решава чрез внедряване на устойчива на грешки архитектура, която осигурява излишък на блокове, които са критични за работата на комутатора.

Един от ключовите компоненти на архитектурата на съвременните комутатори е контролерътASIC (специфична интегрирана схема за приложение). ASIC контролерите са бързи и сравнително евтини силиконови чипове, които са проектирани да извършват специфични операции. Използването на ASIC контролери в архитектурата на комутатора подобрява производителността на системата, тъй като ASIC изпълнява операции в хардуера, така че няма допълнителни разходи, свързани с извличането и интерпретирането на съхранени инструкции. Съвременните ASIC контролери често съдържат 32-битови процесори, блокове памет, включително ROM, RAM, EEPROM, Flash и фърмуер на един и същи чип. Такива ASIC бяха наречени System-on-a-Chip (SoC).

* Умножете по 2 за двустранна работа.

Понастоящем има много видове архитектури на матрица на комутатора. Изборът на матрична архитектура до голяма степен се определя от ролята на комутатора в мрежата и количеството трафик, който той ще трябва да обработва. В действителност матрицата обикновено се изпълнява въз основа на комбинация от две или повече основни архитектури. Помислете за най-често срещаните типове архитектури на превключваща матрица.

Споделена автобусна архитектура

Архитектурата на споделената шина, както подсказва името й, използва шина като споделена среда, която позволява на свързаните с нея I/O устройства (портове) да комуникират. Автобусът се използва в режим на споделяне на времето, т.е. само един източник има право да предава данни през него в даден момент. Достъпът до шина се контролира чрез централизиран арбитър, който дава на източника правото да предава данни.

Прилага се за системи със споделена шина подтерминът "неблокиращ" означава, че сумата от скоростите на матричните портове е по-малка от скоростта на шината. Тези. производителността на системата е ограничена от производителността на шината. Дори ако общата честотна лента е по-ниска от производителността на шината, броят и производителността на I/O устройствата е ограничена от производителността на централизирания арбитър.

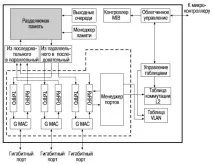

Архитектура на споделената памет

Подобренията в архитектурата на споделената шина доведоха до високопроизводителна архитектураСподелена памет. Архитектурата на споделената памет обикновено се основава на използването на бърза RAM с голям капацитет като споделен буфер в комутационната система за съхраняване на входящите пакети, преди да бъдат предадени. Паметта обикновено е организирана в множество изходни опашки, свързани с едно от I/O устройствата или портовете. За да се осигури неблокираща работа, честотната лента на паметта за операцията "запис" и операцията "четене" трябва да бъде равна на максималната обща честотна лента на всички входни портове.

Типична архитектура на превключвател на споделена памет е показана на фигура 1. 1.13. Входящите пакети се преобразуват от серийни в паралелни и след това се записват в памет с двоен порт. Записът в паметта се извършва в съответствие с принципа на мултиплексирането с разделяне на времето (TDM), така че по всяко време само един входен порт може да постави рамка в споделена клетка с памет. Заглавките на всеки кадър се прехвърлят към контролера на паметта. Въз основа на тази информация, той определя целевия изходен порт и изходната опашка, в която рамката трябва да бъде поставена. Редът, в който изходните кадри ще бъдат прочетени от паметта, се определя от контролера на паметта сизползвайки арбитражния механизъм. Кадрите за четене се изпращат до съответните изходни портове (изходните кадри се демултиплексират във времево разделение, така че само един изходен порт да има достъп до споделената памет), където отново се преобразуват от паралелен в сериен формат.

Едно предимство на използването на споделен буфер за съхранение на пакети е, че той минимизира броя на изходните буфери, необходими за поддържане на ниска степен на загуба на пакети. С централизиран буфер можете да се възползвате от статичното споделяне на буферна памет. Ако трафикът на един от портовете е голям, той може да заема повече буферно пространство, ако споделеният буферен пул не е напълно зает.

Архитектурата на споделената памет има редица недостатъци. Тъй като пакетите се записват и четат от паметта едновременно, тя трябва да има обща честотна лента на порта, т.е. операциите за запис и четене от паметта трябва да се извършват при N (брой портове) пъти скоростта на портовете. защото достъпът до паметта е физически ограничен, необходимостта от ускоряване на работата с N пъти ограничава скалируемостта на архитектурата. Освен това контролерът на паметта трябва да обработва пакети със същата скорост като паметта. Такава задача може да бъде трудна за изпълнение в случай на управление на множество приоритетни класове и сложни операции по планиране. Превключвателите на споделена памет имат една точка на повреда, тъй като добавянето на друг споделен буфер е сложно и скъпо. В резултат на това се използва чиста архитектура на споделена памет за изграждане на комутатори с малък брой портове.