Изследване на мултиплексори и декодери

1. Целта на работата

Изучаване на принципите на организация на типични функционални единици от комбинационен тип: мултиплексори и декодери. Изследване на методи за реализиране на логически функции на мултиплексори и декодери. Придобиване на умения за сглобяване, настройване и изследване на вериги.

2. Принципи на организация на мултиплексори и декодери. Методика за реализиране на логически функции на мултиплексори и декодери

Мултиплексоре комбинирано устройство, предназначено да превключва сигнали от няколко входни шини към една изходна шина в даден ред. С помощта на мултиплексор се осъществява времевото разделяне на информацията, постъпваща по различни канали към един приемник.

Обикновено има един разрешаващ вход и ако има няколко от тях, тогава сигналът на изхода на мултиплексора ще се появи само ако има разрешаващи сигнали на всички строб входове. Наличието на активиращи входове ви позволява да синхронизирате работата на мултиплексора с работата на други възли, както и да увеличите неговия капацитет.

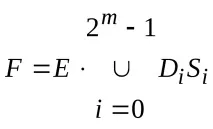

Работата на мултиплексора се описва със следното логическо уравнение

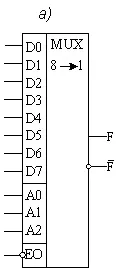

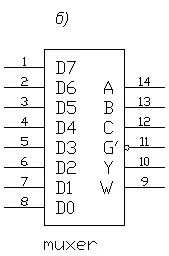

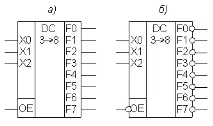

Ориз. 1. Символи на мултиплексора съгласно GOST (a) и в системата DIN (b)

Мултиплексорите, произведени като отделни ИС, имат ограничен брой информационни входове (не повече от 16). За да се увеличи броят на входовете, мултиплексорите се увеличават чрез комбиниране на няколко мултиплексора в пирамидална (дървовидна) или паралелна верига.

Пирамидалните схеми на интегралните мултиплексори са изградени на принципа на каскадата. Броят на етапите се определя от необходимия брой входове на проектирания мултиплексор и броя на входовете на реалните мултиплексорни микросхеми.

F(x0,x1, …,xm–1,xm) =F(x0,x1, …,xm–1, 0)

ПодфункцииF(x0,x1, ….,xm–1, 0) иF(x0,x1, …,xm–1, 1) на всекиi-ти набор от променливи (x0,x1, …,xm–1) или не зависят от стойността на променливаxm, тоест равна на „0” или „1”, или равна на стойносттаxm, или равна на нейната обратна

Ако стойността на посочената функцияF(x0,x1, …,xm–1,xm) наi-тия набор от променливи (x0,x1, …,xm–1) не зависи от аргументаxm, тогаваi-ият информационен вход получава константата „0” или „1”, ако зависи, тогава или сигналът на променливатаxmили неговата инверсия се подава на съответния вход

В случай на изпълнение на функция от повече отm+1, броят на променливите прибягва до специални методи за разширяване на броя на входовете.

Двоичните декодериса комбинационни логически устройства сnвходове (X0,X1, . ,Xn–1) иNизходи (F0,F1,F2… ,FN-1), при което всяко изходно състояние еднозначно съответства на една от възможните комбинации от двоични сигнали на входовете. Ако на входовете на декодера се подадатnе битово двоично число, тогава един (нулев) сигнал се генерира на един от неговите изходи, а нулевият (единичен) сигнал се съхранява на другите изходи. Максималният брой изходи на декодера се определя от стойносттаN= 2n.

Декодерът се нарича пълен, акоN= 2nи непълен, акоNn.

В общия случай веригата на двоичния декодер може да бъде описана с помощта на система от превключващи функции на променливи със следната форма:

;

;

; (2)

;

,

къдетоx0,x1, . ,xn–1са двоични променливи на съответните входове на декодера,F0,F1,F2. ,

В зависимост от метода на структурно изпълнение на тези функции се разграничават матрични и пирамидални декодери. Скоростта на декодера се определя от общото време на забавяне на последователно свързани логически елементи и зависи от броя на етапите на декодера.

Схемата на матричния декодер е изградена на базата на изрази (2), така че всяко уравнение на системата се изпълнява от отделен логически елемент. Когато се конструират непълни матрични декодери, е възможно да се опростят отделните превключващи функции.

Когато се изгражда матричен декодер за голям брой входни променливи, може да е трудно да се приложи схемата поради ограничението на броя на входовете за логически елементи, броя на логическите елементи на чип в пакета на IC и броя на външните щифтове на IC.

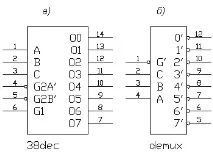

На фиг. Фигура 2 показва условни графични изображения на IC декодера съгласно стандартите на GOST: с директни изходи и сигнал с директна разделителна способност (a) и с обратенизходни сигнали и обратен разрешаващ сигнал (b).

Ориз. 2. Условни графични изображения на IC декодера съгласно стандартите GOST

На фиг. Фигура 3 показва условните графични изображения на ИС на декодера в съответствие със стандарта DIN: с директни изходи (a) и с обратни изходни сигнали (b). В схемата на фиг. 3,aима три активиращи входа: един директен (G1) и два обратни (G2A’ и G2B’).

Ориз. 3. Условни графични изображения на ИС на декодера по DIN стандарт

За увеличаване на битовия капацитет на нискобитовите декодери се използват схеми от пирамидален тип. Характеристика на такава схема е, че входната многобитова дума е разделена на две „полета“. Полето с най-малко значими битове съответства на броя на входовете на наличните декодери. Оставащото поле от цифри се използва за генериране на сигнали, за да се даде възможност за работа на един от декодерите, които декодират полето от най-малко значимите цифри.

Декодерите могат да се използват не само като преобразуватели на двоичен код в унарен код от типа “1отN”, но и за реализиране на комбинационни логически схеми. На декодера, заедно с допълнителни логически елементи, можете да приложите всяка логическа функция, съдържаща доnпроменливи, къдетоnе броят на входовете. Действително, в съответствие с изрази (2), веригата на декодера генерираNот всички възможни minterms отnвходни променливи. Тези изходи, които съответстват на единични стойности на дадена логическа функция, трябва да се комбинират съгласно схемата ИЛИ и ще се получи изпълнението на функцията в SNDF. При практическата реализация на устройството трябва да се има предвид, че основните логически елементи на съществуващата серия са многовходни елементи от типа И-НЕ или ИЛИ-НЕ. Избордекодери с директни или инвертирани изходи, хардуерните разходи могат да бъдат сведени до минимум.

В случай, че броят на променливитеn+1 превишава с един броя на входовете на декодераnи променливатаxnвлияе върху стойностите на дадената функция, могат да се прилагат различни схемни решения. Една от тях е да се използват две ИС за декодиране: едната от тях се стробира на входа за разрешаване чрез сигнал