Линеен декодер

Декодери.

Комбинирани устройства.

Комбинираните устройства са тези, при които състоянието на изходите във всеки момент се определя еднозначно от състоянието на входовете. В този раздел ще разгледаме конструкцията и работата на следните устройства: декодери, мултиплексори, суматори и аритметични логически устройства.

Според начина на схемно изпълнение декодерите се разделят на: линейни, матрични и пирамидални.

Декодерът е комбинирано устройство с n входа и не повече от изхода, което осигурява за всяка стойност на n-битова входна дума появата на активен сигнал само на един от k изхода. Ако броят на изходите на декодера се определя от отношението , тогава декодера се нарича пълен. Ако означим битовете на входната дума , а изходите на декодера ─ , тогава състоянията на изходите на декодера се описват със системата от уравнения:

Системата от уравнения показва, че за да се получат изходните променливи на декодера, е необходимо да се използват елементи „И“, в които броят на входовете се определя от капацитета на входната дума, а броят на тези елементи трябва да бъде равен на броя на уравненията.

Разгледайте примера за изграждане на декодер за двубитова входна дума: n=2 и следователно k=4. Уравненията за декодиране ще изглеждат така:

Уравненията за декодиране показват, че са необходими четири 2I елемента за изграждане на веригата на декодера.

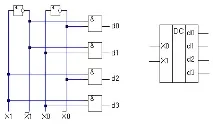

На фиг. 54 е показана схема на декодер за двубитова входна дума и изображение на такъв декодер върху електрически вериги на компютърни устройства. При конструирането на схемата вляво от линията на елементите 2I се изчертават четири линии, към които се подават самите входни променливи (цифрите на входната дума) и техните инверсии, т.е. използва се парафазапредставяне на информация. Връзката на входовете на елементите 2I с входните променливи се извършва в съответствие с уравненията за декодиране и съответно изходите на елементите, които са изходите на декодера, получават обозначенията (d0 - d3). Поради факта, че основата на такъв декодер е ред от логически елементи, той се нарича линеен декодер. За да се намали броят на входовете, е необходимо да се премине към еднофазно представяне на входната информация.

Ориз. 54. Линеен декодер.

Схематично това се прави чрез инсталиране на инвертори между линиите на директни и обратни стойности на входните променливи. Максималното време на забавяне на сигнала, преминаващ през линейния декодер. Удобно е да се използват NAND елементи при изграждане на декодерна верига, докато изходите на декодера ще бъдат активни с ниско ниво. Конструкцията на линейните декодери обаче е ограничена от максималния брой входове на елементите I. Ограничението във възможностите за изграждане на линейни декодери доведе до необходимостта от търсене на други схемни решения за декодери.