Декодери.

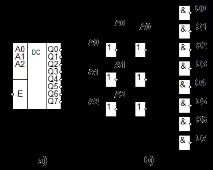

Декодер (DSh) най-често се нарича устройство, което преобразува двоичен код в унарен. От всичкиm изходи на декодера само един има активно ниво, а именно този, чийто номер е равен на двоичното число, подадено на входа. На всички останали изходи на LH нивата на напрежение са неактивни. Обикновено LH имат обърнати изходи. В този случай избраният изход е 0, а всички останали са "1". Унарният код се нарича още код "1 отm ". Условното изображение на LH с обратни изходи е показано на фиг. 3.1а. Вход E ще бъде разгледан по-долу.

Ако LH имаn входове,m изходи и използва всички възможни набори от входни променливи, тогаваm=2 n. Такава ДС се нарича пълна.

Адресните входове на LH обикновено се означават с A0, A1, A2. A(n-1), където индексът на буквата A означава степента на 2. Понякога тези входове са просто номерирани според теглата на битовете: 1, 2, 4, 8, 16. 2 n-1 .

Възможно е формално да се опише работата на LN чрез указване на списък от функции, обработвани от всеки от неговите изходи. Така че за LH (фиг. 3.2, а)

Изпълнението на тези осем израза с помощта на осем тривходни LE 3I-NOT дава най-простата структура LH, нареченалинейна.

Ориз. 3.1. Декодер "1 от 8" с инвертирани изходи.

По-голямата част от линейното LN оборудване обикновено еm n- входни елементи И-НЕ за LN с обърнати изходи илиm n -входни елементи И за LN с директни изходи. Освен това са необходимиn входни променливи инвертори иn буферни инвертори, чиято цел е да намалят до единица коефициента на натоварване, който LN представлява за източника на сигнал. В противен случай всеки източник ще бъде зареден наm/2 входове на NAND или AND елементи.

LH с директни и обратни изходи могат да бъдат изградени,съответно на LE ИЛИ-НЕ и ИЛИ. Общият брой на LE няма да се промени в този случай.

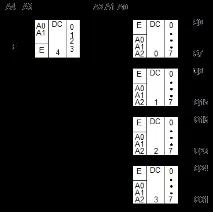

Декодерите обикновено имат разрешаващ вход Е (от enable - разрешавам).

|

Ориз. 3.2. Разрешете въвеждането на декодера.

Ориз. 3.3 Каскадни декодери

Когато се използват елементи 2I-NOT във втория етап, LH изходите ще бъдат инверсни. Те могат да бъдат направени прави, като се построи координатна мрежа върху елементите 2ИЛИ-НЕ; тогава изходите на декодерите на първия етап трябва да бъдат инверсни.

| Ориз. 3.4 Двустепенен координатен декодер |

Горните оценки са валидни само за LH, конструирани директно от LE. При проектирането на блокове от готови микросхеми, когато разходите за оборудване се оценяват не от броя на елементите, а от броя на корпусите, е по-икономично да се изградят дори големи LH според каскадния принцип, като се събират от микросхеми на малки LH за 8 или 16 изхода.

Декодерите се предлагат като отделнимикросхеми, имат буквено обозначение ID. В серията TTL, в която NAND елементите са най-напредналите в технологично отношение, LH обикновено имат обърнати изходи. В серията CMOS, където елементите OR-NOT са не по-малко технологично напреднали от тези на NAND, LN често имат директни изходи. Желанието за по-пълно използване на заключенията на типичните DIP пакети определя размера на LH, произведени под формата на интегрални схеми със среден размер (SIC). Обикновено това са декодери „1 от 8“, „1 от 10“, двоен „1 от 4“, а също и „1 от 16“, но вече в пакета DIP24.

Често няколко активиращи входа се правят в LH микросхеми и тяхната връзка е активиращата комбинация. В същото време е удобно да се увеличи LN, като се използва принципът на каскадата и изграждането на първата каскада за декриптиране не на отделен специален LN, а чрез сглобяването му от конюнкторите на активиращите входове. На фиг. 3.5, и по този начин е изграден LH "1 от 32" от четири микросхеми K555ID7 "1 от 8". Всяка микросхема има три активиращи входа (два обратни и един директен). Разрешение съществува само когато едновременно на обратните входове "нули", а на директния "един".

В микроелектрониката има много често срещана тенденция за производство на микросхеми, способни да изпълняват няколко различни функции: това увеличава търсенето на микросхеми, а увеличаването на продукцията допринася за по-ниски разходи.

Ориз. 3.5 Използване на активиращи входове на декодиращи чипове

а) - първият етап на каскадата LH е изграден върху разрешаващите входове;

б) - универсален декодер чип 2x"1 от 4" и "1 от 8".

A начало = B8H = 1 0 1 0 1 0 0 0 B

A con \u003d BFH \u003d 1 0 1 0 1 1 1 1 B

LH избор LH избор на изход