Хардуерни елементи на компютърната логика

Компютърен логически елемент е част от електронна логическа схема, която изпълнява елементарна логическа функция.

Логическите елементи на компютрите са електронни схеми И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и други (наричани още гейтове), както и тригер.

Използвайки тези схеми, можете да реализирате всяка логическа функция, която описва работата на компютърните устройства. Обикновено вентилите имат от два до осем входа и един или два изхода.

За представяне на двете логически състояния "1" и "0" в гейтовете, техните съответни входни и изходни сигнали имат едно от двете зададени нива на напрежение. Например +5 волта и 0 волта.

Високото ниво обикновено съответства на стойността „истина“ („1“), а ниското ниво съответства на стойността „невярно“ („0“).

Всеки логически елемент има свой символ, който изразява неговата логическа функция, но не показва коя електронна схема е внедрена в него. Това улеснява писането и разбирането на сложни логически схеми.

Работата на логическите елементи е описана с помощта на таблици на истината.

Таблицата на истината е таблично представяне на логическа схема (операция), която изброява всички възможни комбинации от входни стойности на истината (операнди) заедно с изходната стойност на истината (резултат от операцията) за всяка от тези комбинации.

Логически (функционални) диаграми

Веригата И реализира връзката на две или повече булеви стойности.

Символът на структурните схеми на схемата И с два входа е показан на фиг. 1. Таблица на истината - в таблица 1.

| Ориз. 1 | маса 1 |

| х | Y | XCHY |

Единица на изхода на веригата И ще бъде ако и само ако изобщовходовете ще бъдат единици. Когато поне един вход е нула, изходът също ще бъде нула.

Връзката между изхода z на тази верига и входовете x и y се описва от връзката: z = xЧy (чете се като "x и y").

Операцията на свързване върху функционални диаграми се обозначава със знака "&" (чете се като "амперсанд"), което е съкращение от английската дума and.

Веригата ИЛИ реализира дизюнкция на две или повече логически стойности.

Когато поне един вход на веригата ИЛИ е единица, нейният изход също ще бъде единица.

Символът за веригата ИЛИ е показан на фиг. 2. Знакът “1” в диаграмата е от остарялата нотация на дизюнкцията като ">=1" (т.е. стойността на дизюнкцията е равна на единица, ако сумата от стойностите на операндите е по-голяма или равна на 1). Връзката между изхода z на тази верига и входовете x и y се описва от връзката: z = x v y (чете се като "x или y"). Таблицата на истината е в табл. 2.

| Ориз. 2 | таблица 2 |

| х | Y | X срещу Y |

Веригата НЕ (инвертор) изпълнява операцията отрицание. Връзката между входа x на тази верига и изхода z може да бъде написана като z = x, където x се чете като "не x" или "обратно на x".

Ако входът на веригата е 0, тогава изходът е 1. Когато входът е 1, изходът е 0. Символът на инвертора е на Фигура 3, а таблицата на истината е в Таблица. 3.

| Ориз. 3 | Таблица 3 |

| х | х |

Веригата И-НЕ се състои от елемент И и инвертор и отрича резултата от веригата И.

Връзката между изхода z и входовете x и y на веригата се записва по следния начин: , където се чете като "инверсия на x и y".

Символът на веригата И-НЕ е показан на Фигура 4. Таблицата на истинността на схемата И-НЕ е в Таблица. 4.

| Ориз. 4 |

| х | г |

Веригата NOR се състои от елемент OR и инвертор и отрича резултата от веригата OR.

Връзката между изхода z и входовете x и y на веригата се записва по следния начин: , където , се чете като "обратно на x или y". Символът за веригата ИЛИ-НЕ е показан на фиг. 5.

Таблицата на истината на веригата ИЛИ-НЕ е в табл. 5.

| Ориз. 5. |

| х | г | (x v y) |

14.Асинхронен и синхронен тригер [2].

Тригер (тригерна система) - клас електронни устройства, които имат способността да остават в едно от двете стабилни състояния за дълго време и да ги редуват под въздействието на външни сигнали. Всяко състояние на задействане се разпознава лесно по стойността на изходното напрежение. По естеството на действието тригерите принадлежат към импулсни устройства - техните активни елементи (транзистори, лампи) работят в ключов режим и промяната на състоянията трае много кратко време. Този малък период от време обаче може да създаде грешки при определени условия. За това служат синхронните тригери, които ви позволяват да запомните състоянието само на определени интервали

15.Асинхронен D тригер [2].

Асинхронната настройка на D-тригера в единично или нулево състояние се осъществява чрез подаване на взаимно противоположни логически сигнали към входовете /S и /R. В този момент входовете D и C нямат ефект. Останалото е подобно на синхронното. Е тигър за забавяне

16.Синхронен D тригер [2].

D-тригер (D от англ.delay- забавяне [13] [14] [15] или отdata[16] - данни) - запомня състоянието на входа и го издава на изхода. D-джапанките имат катопоне два входа: информационен D и синхронизиращ C. След като активният фронт на синхронизиращия импулс пристигне на вход C, D-тригерът се отваря. Записването на информация в D-тригерите става след затихването на синхронизиращия импулс C. Това е тригер за забавяне

17.Асинхронен T-тригер [2].

Асинхронният T-тригер няма вход за разрешаване на броя - T и включва всеки тактов импулс на вход C.

T-тригер (от английски. Toggle - превключвател) често се нарича тригер за броене, тъй като е най-простият брояч до 2.

18.Синхронен T тригер [2].

Синхронен T-тригер [17], с единица на вход T, за всеки цикъл на вход C променя логическото си състояние на обратното и не променя изходното състояние при нула на вход T. T-тригер може да бъде изграден на JK-тригер, на двустепенен (Master-Slave, MS) D-тригер и на два едностъпални D-тригера и инвертор. T-тригер (от английски. Toggle - превключвател) често се нарича тригер за броене, тъй като е най-простият брояч до 2.

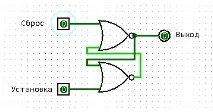

19.Асинхронен RS тригер [2].

Тригер RS, или тригер SR, е тригер, който запазва предишното си състояние при нулеви входове и променя изходното си състояние, когато едно се приложи към един от неговите входове.

RS тригерът се използва за създаване на сигнал с положителни и отрицателни фронтове, отделно контролирани от гейтове, разделени във времето. Също така RS джапанките често се използват за елиминиране на така наречения феномен на отскачане на контакта.

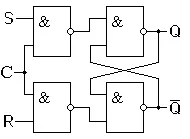

20.Синхронен RS тригер [2].

Веригата RS тригер ви позволява да запомните състоянието на логическата верига, но тъй като в началния момент от време може да възникне преходен процес (в цифровите схеми този процес се наричаопасни състезания), тогава е необходимо да се запомнят състоянията на логическата верига само в определени моменти от времето, когато всички преходни процеси са завършени.

Схемата на синхронен RS тригер съвпада със схемата на едностъпален парафазен (двуфазен) D-тригер, но не и обратното, тъй като комбинациите S=0, R=0 и S=1, R=1 не се използват в парафазен (двуфазен) D-тригер.

21.JK тригер [2].

Тригерът JK се различава от тригера RS главно по това, че елиминира несигурността, която възниква в тригера RS с определена комбинация от входни сигнали.

Универсалността на JK тригера е, че той може да изпълнява функциите на RS-, T- и D-тригери.

Джапанките JK се делят на универсални и комбинирани. Универсалният тригер JK има два информационни входа J и K. На входа J тригерът се настройва на състояние Q=1, /Q=0, а на входа K се установява на състояние Q=0, /Q=1.

22.Половин и носещ суматор [2].

Суматорите се използват за добавяне на числа.

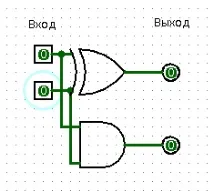

Полуразмере логическа схема с два входа и два изхода (двуцифрен суматор, двоичен суматор). Половината суматор се използва за конструиране на двоични суматори. Полусуматорът ви позволява да изчислите сумата отA+B, къдетоAиBса битове на двоично число, а резултатът ще бъде два битаSиC, къдетоSе битът за сумата по модул 2, аCе битът за пренасяне.

Ако е необходимо да се добавят двоични думи с дължина от два или повече бита, тогава може да се използва серийна връзка на такива суматори, а за два съседни суматора изходъттрансферна един суматор е вход за друг.

23.Скрамблер [2].

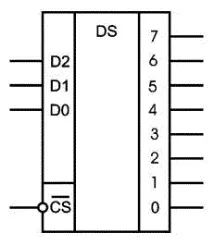

енкодер или енкодер е комбинирано логическо устройство запреобразуване на числа от десетични в двоични. На входовете на енкодера се присвояват десетични стойности, така че активният логически сигнал, приложен към един от входовете, се възприема като съответния десетичен сигнал. Ако енкодерът има n входа, тогава изходът е най-много 2^n. Ако има максимум изходи спрямо входа, тогава той е пълен

Декодер

| Декодерът е устройство, което преобразува цифров сигнал във всякакво кодиране в друга, некодирана форма. |

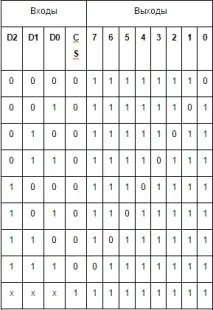

Основната цел на декодера е да избере едно от устройствата, чийто номер идва на входа на декодера. Такива избираеми устройства често са различни цифрови чипове, имащи вход за избор на чип (CS). В този случай сигналите от изходите на декодера се подават към CS входовете на избраните микросхеми. Ето защо активният сигнал на изхода на декодера е сигнал логическа нула. За по-добро разбиране на логиката на декодера, проучете неговата таблица на истината на фигура 25. В тази таблица се появи ново обозначение. Знакът "X" в таблицата на истината означава, че всяка стойност (0 или 1) може да присъства на този вход. В този случай сигналът на нито един от изходите няма да се промени.

Регистър на паметта

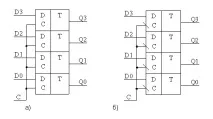

Регистрите на паметта са предназначени за временно съхранение на многобитови двоични кодове. Такива регистри обикновено представляват паралелна група от синхронни D тригери с необходимия капацитет. Така например четирибитов регистър на паметта със статичен контрол се изпълнява съгласно схемата (фиг. 1.8а). Такъв регистър повтаря входната дума, ако часовниковият сигнал C \u003d 1, и помни, фиксира тази дума, ако C \u003d 0. Следователно регистър със статично управление понякога се нарича "прозраченфиксатор." Схемата на регистъра с динамично управление, или както понякога се нарича "регистър тип D", е показана на фиг. 1.8b.