Процесор за систолен удар

Тази архитектура е разработена от Adaptive Solutions, тя е SIMD мултипроцесор с общо предназначение, предназначен за невро приложения. Тъй като чипът не е високоспециализирано устройство, а микропроцесор с общо предназначение, става възможно прилагането на широк набор от алгоритми за обучение и функциониране на невронната мрежа. Чипът има наистина голям капацитет на паметта, позволяващ съхранение на 2M 1-битови мащаби, или 256K 8-битови мащаби, или 128K 16-битови мащаби, равномерно разпределени между 64 процесора. Чиповете могат да формират мултимикропроцесорни системи с различни конфигурации.

Базовият елемент на системата CNAPS е чипът N6400, който се състои от 64 процесорни елемента, свързани с разпределителна шина в режим SIMD. Принципната структура на системата CNAPS е показана на фиг. . Типичната система съдържа контролен чип (Sequencer) и четири процесора N64000 (въпреки че има системи с 8 процесора).

Ориз. 24: Структура на системата CNAPS.

Ориз. Фигура 25: Възел за обработка на процесор N64000

Обработващите възли (PN) са проектирани като обикновени цифрови сигнални процесори, включително суматор и умножител, извършващи аритметични операции с числа с фиксирана запетая. Структурата на обработващия възел PN е показана на Фиг.25. Всеки PN съдържа 4 KB локална статична памет, която се използва за съхраняване на тегла. Размерът на локалната памет е тясно място за големите невронни мрежи, тъй като когато има недостиг на памет, обменът се извършва по шината за излъчване. Производителността пада катастрофално, когато 64 процесорни възли комуникират по обща шина.

Тъй като N64000 работи като микропроцесор с общо предназначение,CNAPS може да реализира широк клас алгоритми за невронни мрежи. За тази архитектура е създаден набор от инструменти, който включва C компилатор с добавки, които ви позволяват да получите код, който се възползва напълно от паралелната архитектура.

Приложение на невросигнални процесори за изграждане на невромедии. Nm6403 невросигнален процесор.

Появата на невросигналните процесори е свързана с успешното използване на цифровите сигнални процесори. Възможностите на DSP не отговарят напълно на задачите, които възникват при моделирането на невронни мрежи. Невросигналните процесори в момента са най-бързото средство за изграждане на невросистеми.

Ядрото на невросигналните процесори е типичен сигнален процесор, а допълнителната логика, внедрена в чипа, осигурява изпълнението на невронни мрежови операции. Пример за невросигнален процесор е NM6403, който реализира архитектурата NeuroMatrix.

Структурата на невропроцесора nm6403.

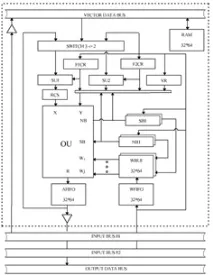

Ядрото nm6403 се състои от два основни блока: 32-битов RISC процесор и 64-битов векторен процесор, който изпълнява векторни операции върху данни с променлива дължина. Има два идентични програмируеми интерфейса за работа с различни видове външна памет и два комуникационни порта, които са хардуерно съвместими с TMS320C4x DSP портове за изграждане на многопроцесорни системи. Общата структура на невропроцесора е показана на фиг. refnm6403.

Ориз. 12: Обща структура на невропроцесора NM6403

Невропроцесорът е проектиран да обработва 32-битови скаларни данни и програмируеми битови данни (опаковани в 64-битови думи). Основните възли на невропроцесора са:

VCP. Векторен копроцесор, който извършва аритметика илогически операции върху 64-битови вектори на пакетирани данни с променлива дължина.

CP0 и CP1. Два еднакви комуникационни порта, напълно съвместими с комуникационния порт на сигналния процесор TMS320C4x.

Невропроцесорът съдържа пет вътрешни шини:

ШИНА ЗА ИЗХОДНИ ДАННИ. Шина, използвана за прехвърляне на данни за запис в локална или глобална външна памет от RISC ядрото, векторния копроцесор и комуникационните портове към програмируемите интерфейсни блокове.

INPUT BUS #1 и INPUT BUS #2. Автобуси, предназначени за прехвърляне на данни и команди, прочетени от локална или глобална външна памет от програмируеми интерфейсни блокове към всеки от основните възли на невропроцесора. В софтуерен режим скаларните данни се прехвърлят само през INPUT BUS #2, а векторните данни се прехвърлят само през INPUT BUS #1. Прехвърлянето на данни в режим DMA и предаването на команди може да се извърши по всяка от тези шини.

Ориз. 13: Ядро на невропроцесор NM6403

Регистри с общо предназначение GR0, . GR7, които образуват регистърен файл;

ALU, което изпълнява една от аритметичните или логически операции върху съдържанието на всички регистри с общо предназначение в един цикъл. Аритметичните операции се извършват върху данни, представени в допълнение от две;

SHIFTER е превключвател, който извършва в един цикъл циклично, логическо или аритметично преместване с произволен брой битове вдясно или вляво от съдържанието на всеки изходен регистър с общо предназначение към шината на първия ALU операнд.

Адресни регистри AR0, . AR3, формиране на регистърен файл;

Блокът за управление (CONTROL UNIT) извършва предварителен анализ и декодиране на команди, избрани от външна памет, генерира сигналиконтролира всички възли на невропроцесора в процеса на конвейерно изпълнение на команди, обработва всички заявки за вътрешни и външни прекъсвания и извършва арбитраж.

Ориз. 14: Векторен копроцесор

Векторният копроцесор (VCP) е основният изчислителен възел на невропроцесора, особено за приложения на невронни мрежи. VCP е фокусиран върху обработка на данни с произволна битова дълбочина от 1 до 64 бита, пакетирани в 64 битови думи. Възможността за избор на битова дълбочина на обработваните данни е отличителна черта на невропроцесора NM6403. Основните VCP възли са:

O.U. Операционна единица, използвана за извършване на аритметични и логически операции върху 64-битови пакетирани думи с данни [(X)/vec] = и [(Y)/vec] =, които се прилагат към входовете X и Y, и тегловната матрица WOPER, която се прилага към входоветеW1,,WJкато J 64-битови думи с опаковани тегла [(W1)/vec] = ,, [(WJ)/vec] = . Резултатът от всяка операция се формира на изхода R като 64-битова пакетирана дума с данни [(R)/vec] = .

RCS. Цикъл надясно, пропуска данни непроменени или завърта надясно с един бит. В един цикъл една дума се измества като отделен операнд, независимо от количеството данни в думата.

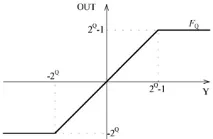

SU1, SU2 Възли, които изпълняват функцията за насищане в хардуера; те се използват за изчисляване на функцията за активиране върху 64-битови думи от пакетирани данни. Общият изглед на реализираната функция за активиране е показан на фиг. .

Ориз. 15: Реализирана функция за активиране

Функцията за активиране се прилага към входния вектор [(X)/vec] преди операцията да бъде изпълнена.

ПРЕВКЛЮЧВАТЕЛ 32. Превключвател 3 в 2 осигурява избордва източника на векторни данни, идващи към входовете на изпълнителните възли на VCP. На входа на всеки нелинеен преобразувател могат да бъдат подавани следните вектори:

вектор на данни с нулеви стойности на всички битове

RAM съдържание от векторната шина за данни VCP (VECTOR DATA BUS).

Съдържание на AFIFO в VCP веригата за обратна връзка

вектор на данни от външна памет

WBUF и WOPER. Памет за претегляне, състояща се от два масива от клетки с памет, всяка с капацитет от 32x64 бита, което позволява матрицата на теглата да бъде съхранена като J 64-битови думи с опаковани тегла. WOPER се използва за съхраняване на матрицата от тегла, използвани в операциите за претеглено сумиране в OU. WBUF се използва за смяна на нова матрица за тегло от WFIFO, докато текущите операции за претеглено сумиране се извършват с помощта на старата матрица за тегло, съхранена в WOPER.

WFIFO Този блок се използва като буфер за натрупване в процеса на размяна на тегловната матрица в WBUF от външна памет. Капацитетът на буфера е 32x64 бита, записът и четенето са 64 битови думи.

AFIFO Този блок се използва като акумулатор и се използва за съхраняване на 32x64 битов резултат от последната векторна инструкция за операция.

RAM.Векторен регистър тип FIFO с капацитет 32x64 бита. Разликата от обикновения FIFO буфер е, че след четене от RAM, съдържанието му не се променя.