SPARC (архитектура на мащабируем процесор)

Лични инструменти

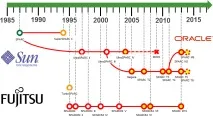

| Sun Microsystems (придобита от Oracle Corporation) |

| 64-битов (32 → 64) |

| 1987 (пратки) |

| V9 (1993) / OSA2015 |

| RISC |

| Регистрирайте се-Регистрирайте се |

| Фиксирана |

| Код на условието |

| Bi (Голям → Bi) |

| 8 KiB (4 KiB → 8 KiB) |

| VIS 1.0, 2.0, 3.0 4.0 |

| Да, и безвъзмездно. |

| 31 (G0 = 0; неглобалните регистри използват регистрационни прозорци) |

| 32 (използваем като 32 с единична точност, 32 с двойна точност или 16 с четворна точност) |

SPARC(ScalableProcessorARChitecture) е 32-битова и 64-битова микропроцесорна архитектура от Sun Microsystems, която се основава на намален набор от инструкции (RISC). Стандартът SPARC е регистриран в IEEE 1754-1994.

Съдържание

Основни характеристики на SPARC архитектурата

Ще разгледаме основните свойства на архитектурата SPARC, използвайки примера на микропроцесора MCST R500:

тагирани инструкции - тагираните инструкции за събиране/изваждане считат двете най-малко значими цифри на техните операнди като тагове;

- инструкции за междупроцесорна синхронизация - едната инструкция извършва непрекъсната операция "четене и последващ запис", другата - непрекъснат "обмен на регистър и памет".

Помислете за структурата на микропроцесорното ядро MCST R500.

Команден буфер (IB).Този модул е предназначен за подаване на заявки за получаване на команди към устройството за управление на паметта, получаване, междинно съхранение и подаване на команди към управляващото устройство. Един от основните компоненти на буфера за инструкции е кешът за инструкции от първо ниво.

Кеширане на инструкции от ниво 1 (I$). Кеш паметта е малка, високоскоростна памет с ниска латентност на достъпа, предназначена да ускорява достъпа до често използвани блокове от основната RAM памет. Капацитетът на I$ кеша е 16 KB. Кешът за инструкции съдържа три блока памет: памет за данни, памет за етикети и памет за стареене. Механизмът за стареене определя кои блокове в паметта за данни могат да бъдат заменени. I$ кешът е вграден в ядрото и се намира на същия чип.

Управляващият блок (CU)е проектиран да решава следните задачи:

- дешифриране на инструкции, идващи от кешаI$инструкции;

- формиране на стартирания и блокиране на устройства;

- организиране на четене на операнди от целочислениIRFи реалниFRFрегистрови файлове за съответните аритметични логически устройства (ALU) и записване на резултатите в съответните регистрови файлове;

- байпас контрол [1] на устройството за целочислени команди.

Регистърният файле микропроцесорен модул, който реализира своите регистри под формата на масив от клетки на паметта. В ядрото на процесора R500 има 2 регистрационни файла: за целочислени данни и за реални данни.

Регистърен файл с целочислени данни (IRF).ВIRFданните от целочислен тип се съхраняват за обработкаоперации. Регистърният файл съдържа 136 регистъра от 32 бита (8 прозореца от 16 регистъра и 1 прозорец от 8 глобални регистъра).

Регистърен файл с реални данни (FRF).Този модул съхранява данни от реален тип. Регистърният файлFRFсъдържа 32 регистъра с 32-битови данни. В този случай модулът може да се интерпретира в програмите като набор от 32 едноформатни регистъра (32-битов капацитет), или като 16 двуформатни регистъра (64-битов капацитет), или като смесен набор от регистри от първи и втори тип.

Аритметичното логическо устройство на реални команди (FPU)е предназначено за изпълнение на команди с операции върху реални числа, както и команди за умножение и деление на цели числа.

Единикът за управление на паметта (MMU)изпълнява следните функции: