Типове клъстери 19 стр

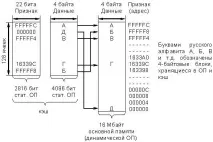

Фиг.22.6. Организация на кеша

Както вече беше отбелязано, прехвърлянето на информация от OP към кеш паметта и обратно се извършва на цели блокове. За тази цел OP също е разделен на блокове от 2 до 16 байта. Ако исканата от процесора информация не е в кеша, тогава кеш контролерът актуализира съдържанието на кеша в цял блок. Размерът на блока е много важен параметър, който определя ефективността на кеша. В 32-битовите системи контролерът изпраща набор от данни от 2-4 думи (4-16 байта) като блок. Дори ако бъде поискана една дума, прехвърлянето на блок все още се извършва. С увеличаването на блока модификацията на кеша се забавя, но коефициентът на попадения се увеличава. И така, увеличаването на блока от 4 байта на 8 увеличава коефициента на попадение с няколко процента. Това обаче поставя по-малко блокове в кеша. И с намаляване на броя на блоковете, вероятността от операции за прехвърляне на блокове между кеша и RAM се увеличава, така че трябва да изберете оптималното (както вече беше отбелязано). Обикновено в изчислителните системи, базирани на I80386, I82385, работата на кеш паметта е организирана по такъв начин, че вероятността за успешен достъп достига 0,95.

При обработката на различни класове задачи най-голямата ефективност на системата за кеш памет се постига с помощта на различни структури, а именно:напълно асоциативен кеш,директно картографиран кешимножествен асоциативен кеш. Всяка от тези структури има своите предимства и недостатъци. По принцип всички тези структури се поддържат от I82385 кеш контролера с някои ограничения. Нека разгледаме тези структури по-подробно, като приемем, че капацитетът на RAM на изчислителната система е 16 MB.

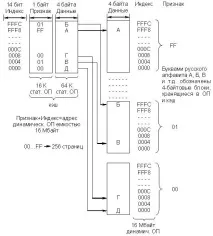

- Напълно асоциативен кеш(фиг. 22.7)

Фиг.22.7.Организация на напълно асоциативен кеш

- Директно картографиран кеш(фиг. 22.8)

Фиг.22.8. Директно картографирана организация на кеша

Опростен алгоритъм за достъп до паметта на процесора е следният:

- 14-битовият индекс казва на кеш контролера коя от 16 KB еднобайтови клетки в банката с характеристики трябва да бъде проверена:

- ако функцията, поискана от процесора, съвпада с функцията в банката с функции, настъпило есъвпадение. Ако не, се осъществява достъп до OP и функцията и данните в кеша се заменят с данните, получени от OP.

Разгледаната структура на кеша се различава от предишната (напълно асоциативна) по това, че няма несигурност в разположението на блока с данни. Адресът (индексът) се посочва директно в заявката на процесора и трябва да се сравни само знакът. Товаускорявапроцеса на обмен.

Този проблем може да бъде избегнат, като се позволи на всяка клетка в OP да бъде насочена, ако е необходимо, не къмедна, а къмдве или повечекеш клетки. Това увеличава коефициента на попадение, но също така усложнява алгоритъма за достъп до паметта.

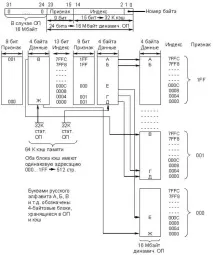

- Двупосочен множествен асоциативен кеш(фиг. 22.9)

Множественият асоциативен кеш е междинен между напълно асоциативен кеш и директно картографиран кеш. От горната структурна диаграма следва, че банката с характеристики и банката с данни, използвани в кеша с директно картографиране, в този случай са разделени на два блока, всеки от които има собствена банка с характеристики и банка с данни с капацитет от 32 KB.

Фиг.22.9. Организация на двупосочен множествен асоциативен кеш

В заключение трябва да се отбележи, че в изчислителните системи, базирани на процесора I80386 в стандартна конфигурацияКеш контролерът I82385 поддържа двупосочен множествен асоциативен кеш и директно картографиран кеш.

В съвременните компютри, изградени на базата на мощни процесори, има допълнително разслояване на вътрешната памет и преди всичко разслояване на кеша. Бързият L1 кеш в чипа и "по-бавният" външен L2 кеш са задължителни компоненти на всички съвременни IBM PC. Взаимодействието на кеша на двете нива се основава на принципи, подобни на принципите на взаимодействие на други йерархични слоеве на паметта - минимизиране на броя на повикванията от по-бърз слой към по-бавен. По-нататъшното увеличаване на производителността на процесорите неизбежно ще доведе до допълнително разслояване на кеш паметта на компютъра.

22.3. Динамично разпределение на паметта. Виртуална памет

В много случаи големи изпълними програми и структури от данни не могат да бъдат напълно поставени в RAM, тъй като капацитетът на съществуващата RAM е ограничен. Този проблем е особено остър в многопрограмни, многопотребителски системи, които, грубо казано, изпълняват няколко програми едновременно. Естествено, във всеки момент компютърът изпълнява команда на една програма. Въпреки това, всеки път, когато изпълнението на определена програма от процесора е спряно поради необходимостта от извършване, например, на IO операция, процесорът продължава да обработва друга програма, която е готова за изпълнение. Предполага се, че едновременно в ОП има няколко програми, които могат да бъдат в активно състояние, състояние на готовност или изчакване. Въпреки това, няма фундаментална необходимост всички програми (или една голяма програма) да бъдат в OP, тъй като по всяко време работата на програмата е концентрирана върхуопределени сравнително малки площи. По този начин в EP трябва да се съхраняват само части от програми, използвани в даден период, а неизползваните части (програми или програми) могат да се съхраняват във външната памет на компютъра (EP).

Прилагането на динамично разпределение само в софтуера би довело до значителни загуби на компютърно време, така че за тази цел се използва и хардуер.

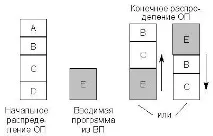

При разглеждания метод за динамично разпределение на паметтасвободната паметможе да се състои ототкъснати области(фрагментацияна паметта) и за да влезете в желаната програма, може да е необходимо да преместите съдържанието на паметта. Това може да се илюстрира с пример в

Фиг.22.10. Пример за разпределение на паметта

Първоначално RAM се разпределя между програмите A, B, C, D. Програмите A и D в момента са най-малко активни и могат да се разглеждат като кандидати за премахване във външна памет. Ако нововъведената програма E е по-голяма от някоя от програмите A и D, тогава за да я поставите в паметта, е необходимо да преместите програмите B и C "нагоре" или "надолу". Това движение е свързано със загубата на време. Освен това в редица предишни операционни системи подобен ход изискваше повторно редактиране на връзките в програмата и презареждане на програмата.

Отбелязаните недостатъци в разпределението на RAM липсват привиртуалнатапамет със страница организация.

22.3.1. Виртуална памет

Новозаредената програма в OP може да бъде насочена към всички свободни в момента физически страници, независимо дали са разположени в ред или не. Няма нужда да премествате информация в останалата част от паметта. Пагинирането позволява по-рационаленобмен на информация между VP и OP, тъй катостраницата на програмата не трябва да се зарежда, докато не е наистина необходима (което означава, че обменът на малки блокове информация между VI и OP може да се извърши без забележимо намаляване на производителността на процесора). Първо, началната страница на програмата се зарежда в OP и управлението се прехвърля към нея. Ако по време на обработката на програмата се направи опит за избор на думи от друга страница, тогава се извършва автоматично извикване на операционната система, която зарежда необходимата страница. Това се случва по време на изпълнението на цялата програма, докато ненужните модифицирани страници на програмата се преместват от OP към VI. Операцията по заместване (заместване) на страници в ОП се наричаswapping(swapping), а частта от диска, предназначена за нуждите на виртуалната памет, еswap file(swap file). Размерът на този файл и следователно максималният обем виртуална памет за конкретен компютър зависи от общото пространство на твърдия диск и вида на инсталираната операционна система.

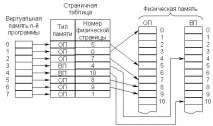

Съответствието между виртуалната и физическата памет се установява оттаблицата на страниците, а физическите страници могат да се съдържат в текущия момент както в RAM, така и във VP.

Опростена диаграма на страниране на паметта е показана в

Фиг.22.11. Опростена схема за страниране

Ако таблицата на страниците сочи местоположението на необходимата информация във външната памет (EP), тогава достъпът до OP не може да се осъществи веднага, тъй като операционната система трябва да организира зареждането на необходимата страница в OP от EP.

За всяка от програмите, обработвани в многопрограмен режим, се организира собствена виртуална памет и се създава собствена таблица на страниците, докато всички програми споделят еднафизическа памет (OP и VP).

22.3.2. Организация на паметта на сегментите

Процесорът I80386 поддържа 16 000 сегмента с различни размери. Размерът на всеки сегмент може да бъде до 4 GB, което ви позволява да реализирате управление на виртуална памет с капацитет до 64 TB (в режим на многозадачност, 16 000 сегмента за всяка нова задача).

Все пак трябва да се има предвид, чевиртуалната паметкатофизическиобектне съществува(за разлика от кеш паметта), въпреки че има известна хардуерна поддръжка. Виртуалната памет е "творение" на операционната система и следователно законите на нейното функциониране зависят от конкретния тип операционна система.

В допълнение, производителите в процеса на подобряване на хардуера са склонни да запазят приемствеността на поколенията процесори. Това позволява използването в нови модели на вече написан софтуер за изчислителни системи, изградени на базата на по-ранни модели процесори, но прави алгоритмите за достъп до паметта по-консервативни. Тази приемственост се постига главно по два начина:

- Създаване на нови модели процесори, чиито разширени системи за инструкции "покриват" системите за инструкции на предходните модели. И така, всички процесори на Intel от семейството I80x86, включително 32-битовите (I80386, I80486, Pentium, Pentium Pro), включват както подмножество от системата за инструкции, така и архитектурата на по-ниските модели, като се започне от базовия модел I8088;

22.4. Контролни въпроси

1. Маркирана организация на паметта.

2. Използване на дескриптори.

3. Описание на двумерен масив от данни чрез дървовидна структура от дескриптори.

4. Методи за оптимизиране на обмена процесор-памет.

5. Основни принципи на процедурите на конвейерния контуризпълнение на команда.

6. Използване на стратификация на паметта.

7. Буфериране на паметта. Схема на свързване на буферна памет.

8. Взаимодействие между кеша и ОП. Проходен и заден вход.

9. Организация на напълно асоциативен кеш.

10. Организация на кеша с директно картографиране.

11. Организация на двувходов множествен асоциативен кеш.

12. Динамично разпределение на паметта. виртуална памет.

13. Опростена схема на организация на пейджинг паметта.

15. Сегментно-странична организация на паметта.

Лекция 23

Ако няколко независими програми могат да пребивават в паметта едновременно, са необходими специални мерки за предотвратяване или ограничаване на достъпа на една програма до области на паметта, използвани от други програми. Подобен проблем възниква при изпълнение на отделни модули на големи програми. Причините за неоторизиран достъп до чужди зони на паметта могат да бъдат внезапно прекратяване на изпълнението на програмата от процесора в резултат на повреда в компютърния хардуер, влизане в безкраен команден цикъл, грешки в потребителската програма, особено при нейното отстраняване на грешки. Последствията от такива повреди при нормално функциониращи компютри са особено опасни, ако програмите на операционната система са унищожени, тъй като след това компютърната система може да започне да се държи непредсказуемо.

За да предотвратите унищожаването на някои програми от други, достатъчно е да защитите областта на паметта на тази програма от опити за запис в нея от други програми, а в някои случаи и от вашата собствена програма (защита от запис). Това позволява на други програми да имат достъп до тази област на паметта, за да четат данни.