23 Схеми за изместване на ниво

23 Схеми за изместване на нивото на постоянен потенциал

Многостепенната конструкция на DC усилватели, включително повечето аналогови микросхеми, обикновено се свързва с използването на конфигурации на вериги в усилващите пътища, които осигуряват намаляване (изместване) на постоянни потенциали в междукаскадни вериги. Необходимостта от включване на схема за изместване на нивото (SSU) се дължи на факта, че в микросхемите производството наpnpтранзистори с добри характеристики е свързано с определени технологични трудности. В тази връзка в аналоговите микросхеми те се опитват да избегнат използването на транзистори от този тип и, съответно, пътеки с верижни конструкции, редуващи се по вид проводимост.

При каскади от OE и OB на транзисториnppот структурата, постоянният потенциал на изхода винаги е по-висок от входа. В резултат на това в многоетапен път с директни междустъпални връзки се получава многостепенно увеличение на потенциалните нива от вход към изход. В резултат на това за нормалната работа на многостъпален път без SSU са необходими захранващи устройства с повишена стойност на напрежението.

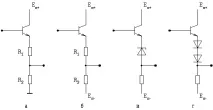

Основната цел на SSU е да намали постоянния потенциал с минимално затихване на сигнала. Обикновено, едновременно с изпълнението на тази функция, SSU действа като буфер, който намалява влиянието на следващата каскада върху предишната. За изпълнение на тази допълнителна функция на входа на SSU е включен повторител на напрежението. Най-простите опции за конструиране на SSU са показани на фигура 1.

Фигура 1. Най-простите схеми за преместване на ниво

В SSU на фигура 1а е невъзможно да се получат потенциални намаления до малки и нулеви стойности, тъй като в тази верига резистивният делителедин терминал е свързан към точката на нулев потенциал. Освен това в него има значително затихване на сигнала. Тези недостатъци са частично лишени от схемата на фигура 1b, в която долният извод на резистивния делител се захранва от източник на напрежение с отрицателна полярност. Коефициентите на предаване, близки до единица, имат веригите на фигури 1c и d, в които сигналното напрежение се предава през двуизводна мрежа с малко диференциално съпротивление.

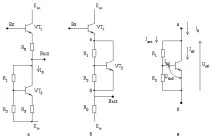

Фигура 2а показва SSU с GTS. Поради големия изходен динамичен импеданс на HTS, коефициентът на предаване в него е близък до единица.

Фигура 2 Схеми за изместване на ниво

Във веригата на фигура 2b се използва верига, базирана на биполярен транзисторVT2, като основна връзка за изместване на потенциала, със стабилизиращо напрежениеUct =Ube0 / , където »R2 / (R1 +R2). Приближението на последното съотношение се дължи на факта, че то не отчита шунтиращия ефект върху резистораR2 на DC входното съпротивление на прехода база-емитерRbe =Ube0 /Ib0 на транзистора. Приемливостта на такова предположение е изпълнена при условия, когато делителният токIdiv, протичащ през резистораR2, значително надвишава базовия токIb0 на транзистораVT2. При тези условия веригата на Фигура 2с осигурява спад на постоянно напрежение между клемиa-bв съответствие с формулата

Нека определим големината на токаI0, протичащ във възелаа. Според уравнението на Еберс-Мол и последната връзка

Обикновено в диаграмата на фигура 2b условиетоIdel е изпълнено.Съседни файлове в папката Lektsionnye_materialy_osen_2013 (1)

-

#