ФТФ 5 семестър. СОКОЛОВ - 40

Изолация на полупроводникови IC компоненти

Полупроводниковите IC елементи трябва да бъдат изолирани един от друг. Това е необходимо, така че необходимите връзки да се извършват само чрез метално окабеляване. Методите за изолация могат да бъдат разделени на три групи:

- изолация чрез обратно предубеденоp‑nсъединение;

- изопланарен метод, който е комбиниран метод.

1.2.9.1. Изолиране чрез обратно предубеденоp‑nсъединение

Методът се основава на използването на епитаксиалнаn-pструктура със скритn+ слой, получен вp-Si субстрат преди отглеждане на епитаксиален филмn-от тип проводимост.

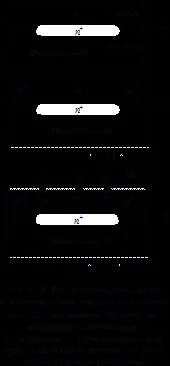

Полученият детайл (фиг. 1.37,a) се използва за получаване наn-p-nбиполярни транзистори. Последователността на производство на биполярен транзистор с изолационен обратенp-nпреход е показан на фиг.1.37,bиc.

За изолиране по краищата на скритияn+ слой се извършва изолираща разделителна дифузия на акцепторния примес през маската до цялата дълбочина на епитаксиалнияn-слой.

В резултат на разделителна дифузия се създава колан от област сp+ тип проводимост, електрически свързана към субстрат сp-тип проводимост. „Островите“ от типn, оставащи в епитаксиалния слой след разделителната дифузия, се наричат „джобове“ (фиг. 1.37,b).

След това в изолирани зони - джобове се извършва базова и емитерна дифузия и повърхността се метализира, както е показано на фиг. 1.37,in.

За изолация, отрицателно блокиращо напрежение –Up се прилага къмp-тип субстрат спрямо колектора на транзистора.

1.2.9.3. Диелектрична изолация

За диелектрикизолацията най-често използва силициев диоксид SiO2. Могат да се използват други диелектрични материали, съвместими със силициевата IC технология (напр. Si3N4, Al2O3).

В сравнение с изолацията на преходаp‑nс обратно отклонение, диелектричната изолация намалява капацитета между IC елементите и субстрата и намалява тока на утечка на изолацията с порядък. В тази връзка честотните им характеристики са подобрени. В допълнение, изолираните с диелектрик ИС имат по-високо пробивно напрежение и по-добра радиационна устойчивост. Недостатъкът на диелектричната изолация е лошото разсейване на топлината поради ниската топлопроводимост на изолационния слой.

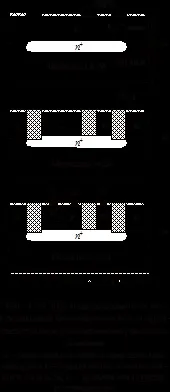

Исторически, първият метод за изолация с диелектрик е така наречениятепичен процес. Основните операции на този процес са показани на фигура 1.39.

Като изходен материал се използва епитаксиална силициева структураn+ -nс дебелина на епитаксиалния филм от 2…3 µm (фиг.1.39,а).

През маската в плочата се гравират жлебове с дълбочина 10…15 µm, след което получената релефна повърхност се окислява със SiO2 (фиг.1.39,b).

Освен това върху окислената релефна повърхност (от страната на епитаксиалния слой) в специална инсталация за отлагане се изгражда дебел (200 ... 300 микрона) слой от поликристален силиций (фиг. 1.39,c).

След това оригиналната плоча отn-тип се обръща и субстратът отn-тип проводимост се смила до пълната дебелина, до дъното на жлебовете. В резултат на това се получават джобове типnсъс скрит слойn+, разположен върху поликристален субстрат. Изолацията на елементите се осигурява от слой SiO2 оксид (фиг.1.39,d).

В крайните етапи транзисторите се произвеждат чрез дифузия наn- иp-примеси вемитер, колектор и базови области и метализация (Фиг.1.39,e).

Значителен недостатък на епичния метод на изолация с диелектрик е необходимостта от прецизно смилане с грешка по цялата повърхност в рамките на 1 ... 2 μm.

Технология Silicon on Sapphire.Така наречената технология Silicon on Sapphire (Silicon on Sapphire) стана широко разпространена. Технологията SPS принадлежи към класа технологии с въздушна изолация. Изходният материал е сапфирена или алуминиево-магнезиева шпинелна подложка с нараснал върху тяхn-Si епитаксиален филм с дебелина 1…3 µm (фиг.1.40,а). Това е възможно, тъй като изкуственият сапфир α-Al2O3 или шпинелът MgO·Al2O3 има параметър на кристалната решетка, близък до този на силиция (aSi=0,543072 nm). В допълнение, тези кристални структури се характеризират с изоморфизма на кристалните решетки.

При производството на транзистори, използващи SOS технология, първо, примесите се дифузират в епитаксиалния силициев слой от типn, за да се създадат структуриn-p-n, равномерно разпределени по повърхността на кристала. След товаnот слоя Si се гравира до сапфир, така че да се образуват силициеви острови-джобове, със структураn-p-nот биполярни транзистори (фиг.1.40,b).

Тези джобове са изолирани един от друг с диелектрик - сапфир, от долната страна, а отстрани - с въздух.

SOS технологията намира приложение в техниката за създаване на MOS устройства, диференциални или операционни усилватели, микровълнови и високочестотни интегрални схеми. Това се дължи на факта, че веригите върху диелектричен субстрат се характеризират с ниски стойности на паразитни капацитети (до 0,1–0,2pF/mm 2 ) и работни честоти до 4 GHz.

1.2.9.4. Комбинирани методи за изолация

Тези методи съчетават методите на изолиране чрез обратно предубеденоp‑nсъединение и изолиране чрез диелектрик. Изопланарният процес се използва главно за изолиране на IC елементи при производството на интегрални схеми с памет.

Понастоящем най-разпространеният комбиниран метод е така нареченатаизопланарна технология (isoplanar).

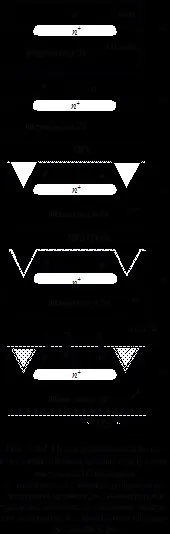

Изопланарният процес се основава на локално чрез окисляване на тънък (1…2 µm)n-тип епитаксиален силициев слой съсn+-тип скрит слой, отгледан върхуp-тип субстрат. Технологията на производство е както следва.

Оригиналната пластина е маскирана със слой от силициев нитрид Si3N4, в който са създадени прозорци за последващо локално окисляване наn-епитаксиалния слой (фиг.1.41,а)

Последващо окисляване на епитаксиалния слойn-Si, за да се създадат изолирани области (Фиг.1.41,b)

В резултат на окисление, епитаксиалниятn-слой е разделен на два джоба отn-тип, точно както при метода на изолация чрез обратно предубеденоp-nсъединение. Двата джоба са свързани чрез скритn+ -слой. В този случай обаче страничните изолационни слоеве не са полупроводникови, а диелектрични. Долните части на джобовете също са разделени отp‑nкръстовища. Ето защо изопланарният метод спада към комбинираните методи.

Последната част от изопланарния процес е създаването на емитерни и базови области в основната част на гнездото и извеждането на колекторния проводник от страничния джоб.

Метод на изолация с V-образен канал.За достатъчно дебели епитаксиални слоеве, например до 3µm, се използва вариант на изопланарния метод - методът на изолиране на V-бразда (метод на вертикално ецване, метод VIP).

При този метод, вместо чрез окисляване на епитаксиалния слой, се използва методът на анизотропно ецване на силиций, последвано от покриване на получените канали с SiO2 + Si3N4 оксиди. Подложката е ориентирана в посока . В тази посока ецването протича 30 пъти по-бързо, отколкото по страничните повърхности на жлеба, ориентирани в посока . Ъгълът между посоките и е 61,5 0 . Получените V-образни канали спестяват площта, необходима за изолиране на елементите.

Диаграмата на процеса е показана на фиг. 1.42,a-e.

1. Като заготовка се използва пластинаp--Si, ориентирана в посока , с епитаксиален слой от типnи скрити слоеве от типn+ -проводимост (фиг. 1.42,а).

2. С помощта на дифузия на акцепторен примес се създава базова област сp-тип проводимост (фиг. 1.42,b).

3. Повърхността на плочата е защитена със слой от SiO2 чрез маска. Прозорците се отварят в маската. Размерите на прозореца в маската са направени така, че лицата (111) на V-жлебовете да се събират точно под границата на епитаксиалния слой.

Ширината на прозореца се изчислява по формулата, къдетоdе дълбочината на канала. Обикновеноd=4…5 µm,b=5,6…7 µm. Следователно загубата на площ на матрицата за изолация е наистина много малка. Анизотропното ецване на повърхността на Si се извършва през прозорците в маската (фиг. 1.42,c).

4. След това повърхността на плочата е допълнително защитена със слой от SiO2 + Si3N4 (фиг. 1.42,d).

5. Жлебовете се запълват с поликристален силиций, повърхността на плочата се полира, след което се оформят емитерната и колекторната области на транзистора и проводниците (фиг.1.42,e).

VIP методът осигурява по-висок процент от добива на подходящи ИС и значително по-висока плътност на елементите, отколкото при използване на изопланарен метод.