L_Двустепенни тригери

Тактовите логически схеми, в допълнение към информационните входове, имат един или повече входове за синхронизация. Импулсите за синхронизиране на часовника ви позволяват да разпространявате във времето преходни процеси в различни каскади от логически устройства, за да избегнете фалшиви положителни резултати в точки на превключване. Най-простите примери са синхронните RS- и D-тригери. Доста често се използват две тактови последователности от тактови импулси с еднаква честота, но изместени с половин период. В сложни системи могат да се използват повече тактови последователности. Устройствата с тактова логика са по-бавни, по-сложни и консумират повече енергия, но са по-стабилни.

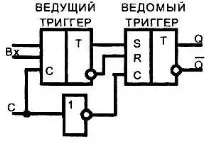

Тригерите с двустепенно съхранение на информация се състоят от два тригера. Първият се нарича лидер, вторият - роб m (фиг. 1).

И двата тригера са синхронни RS тригери, но имат противоположни синхронизиращи входове. Главният тригер се задейства, когатоC= 1, има директен синхронизиращ вход, а подчиненият, когатоC= 0. За тази цел тактовият импулс се инвертира.

На първия етап, когато информацията се записва в главния тригер, подчиненият се дезактивира и продължава да поддържа предишното състояние. Когато часовникът приключи, главният тригер преминава в режим на задържане и състоянието му се презаписва в подчинения тригер. По този начин има поетапно записване на информация.

При двустепенен тригер се елиминира противоречието между процесите на съхраняване на стара и получаване на нова информация. Това дава възможност за изграждане на синхронни автомати без опасни временни състояния, за да се изключат предпоставките за режим на генериране. Позволява да се осигури висока надеждност на функционирането на тригерите свътрешни вериги за обратна връзка. В същото време веригите на тези джапанки са по-сложни от веригите на джапанките с динамичен вход и скоростта е по-ниска.

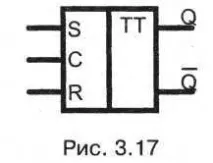

Често двустепенният тригер се нарича MS тригер от английските думи"master"и"slave"- главен и подчинен. В електрическите схеми двустепенните тригери се означават с двойната буква(TT)фиг. 2.

Според структурата на двустепенния тригер могат да бъдат изградени всякакви видове тригери.

ДжапанкитеJKса двустепенни универсални синхронни тригери. Универсалността се състои в това, че на тяхна база можете да направите всеки друг тип логически тригериRS,D, T.

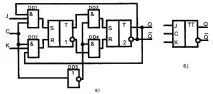

ТригерътJKе двустепенен тригер с допълнителна обратна връзка, която предотвратява появата на забранени комбинации. За целта неговият входен контрол на първия тригер е изграден върху 3I елемента (DD1-DD2) и има два допълнителни входа, към които се прилага обратна връзка. На фиг. 3 показва подробна диаграма и условно изображение на тригераJK-.

Когато логическото ниво е 0 на вход C, първиятRS-тригер не отговаря на сигналите на входоветеJиKКогато C = 1 е приложен към входа, първиятRS-тригер се настройва в състояние, определено от сигналите наJиKвходовете. В този случай връзката между тригеритеRS-се прекратява, тъй като елементите ИDD3-DD4са поставени в нулево състояние. Повторното прилагане на сигнал C = 0 към входа за синхронизиране наJK-тригера води до прекъсване на връзката на първияRS-тригер от входните сигнали порадиDD1,DD2.елементите. Въпреки това, когатоC= 0, логическа единица и състоянието на първия 5>RS -тригер е превишено ritten по време навторо.

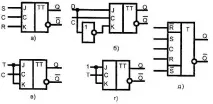

Въз основа наJK-тригера може да се изгради всеки друг тригер (фиг. 4). На фиг.4, a - синхроненRS-тригер, на фиг.4, b -D-тригер, на фиг.4, c - синхроненT-тригер, на фиг.4, d - асинхроненT-тригер.

ТригерътJK, подобно на други видове тригери, може допълнително да има входове за първоначална настройка (фиг.4, д), които са обратни по отношение на входоветеJ.K.

JK-джапанките са по-сложни джапанки, съдържат по-голям брой елементи, така че консумацията на енергия наPpotе голяма. Мерките, предприети за намаляване на консумацията на енергия, често водят до влошаване на честотните свойства.JK-тригерът, поради своята гъвкавост и липсата на забранени комбинации, се използва широко в цифровата технология.