Лекции - 6 стр

U pom + = U out 0 .max – U in 0 .max

За токове, на първо място, се посочва токът на консумация I pot, който също е необходим за определяне на мощността, консумирана от елемента, изчислена като произведение на захранващото напрежение на елемента и тока, консумиран от него.

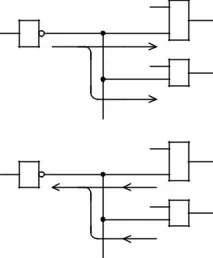

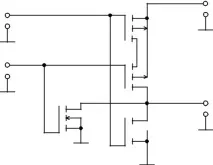

Следните четири текущи стойности сред най-важните статични параметри са входни и изходни токове в двете логически състояния: I in 0, I in 1, I out 0, I out 1. При високо ниво на изходно напрежение токът изтича и веригите на натоварване поглъщат ток (Фигура 1.14, а).

Фигура 1.14 - Посоката на изходния и входния ток при високо ниво на изходното напрежение (а) и ниско ниво - (б)

При ниско ниво на изходно напрежение токът на натоварване протича в този елемент и токовете излизат от входните вериги (Фигура 1.14, b). Следователно входните и изходните токове в различни логически състояния протичат в различни посоки. Познавайки токовете I out 1 .max и I out 0 .max, характеризиращи възможностите на сигнала, и консумираните токове I in 1 .max и I in 0 .max могат да бъдат консумирани

контролирайте спазването на ограниченията на натоварването, което е задължително за всички елементи на веригата на цифрово устройство.

Освен това статичните параметри включват:

– Коефициентът на разклоняване на изхода K пъти характеризира товароносимостта на логическия елемент и определя броя на входовете на подобни елементи, които могат да бъдат свързани към изхода на този елемент. Колкото по-висока е товароносимостта на елементите, толкова по-малко елементи може да са необходими при изграждането на цифрово устройство. От фигура 1.14 следва, че изходният коефициент на разклоняване K пъти може да се определи по формулата:

K пъти \u003d I out / I in.

По формула (1.34) можеопределяне на допустимата стойност на изходния ток I out при липса на референтни данни;

– Коефициентът на комбиниране на входа K о определя броя на входовете на логическата

логически елемент, предназначен да предоставя логически аргументи. Елементите с голям коефициент на обединяване на входа имат повече функционалност;

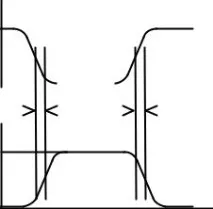

Най-важният динамичен параметър е скоростта на логическите елементи. Оценява се чрез забавянето на разпространението на сигнала от входа към изхода на логическия елемент при включено t 1.0 zd.r и изключено t 0.1 zd.r (логическият елемент е включен, ако изходът му е log. 0 и обратно). Времевите диаграми за превключване на инвертиращия логически елемент са показани на фигура 1.15.

0,5

0,5

Фигура 1.15 - Времеви диаграми на входно и изходно напрежение при превключване на инвертиращ логически елемент

Времето на забавяне се измерва на изхода по отношение на входа на нива от 0,5 от стойностите на напрежението в стационарно състояние (Фигура 1.15).

Често се използва средното забавяне на разпространението:

= 0.5((t 0.1 zd.r + t 1.0 zd.r ) , [ns]. Колкото по-малък е този параметър, толкова по-висока е скоростта на логическия елемент. Този параметър се използва при изчисляване на забавянето на разпространението на сигнали в сложни логически схеми

Скоростта на цифровите устройства също се влияе от товарен капацитет и паразитен монтажен капацитет, които изискват време за презареждане. Референтните данни показват входния и изходния капацитет на логическите елементи, което дава възможност да се изчислят капацитетите на натоварване във възлите на веригата. Максимално допустимият капацитет показва границата, при която е гарантирана работата на логическия елемент.

Мощността, консумирана от логическите елементи, се разделя настатичен и динамичен. Статичната мощност се консумира от елемент, който не е

превключватели, това е средната консумация на енергия, определена по формулата:

P пот cf 0,5(P 0 P 1 ), [mW],

където P 0 е мощността, консумирана от захранването при ниско ниво на изходното напрежение, а P 1 е при високо ниво.

При превключване се изразходва допълнителна динамична мощност, която е пропорционална на честотата на превключване. По този начин, пълното

консумацията на енергия зависи от честотата на превключване

елемент. Следователно скоростта на логическия елемент и общата консумация на енергия са взаимосвързани: с увеличаване на скоростта консумацията на енергия се увеличава.

Превключваща енергия E на логически елемент от един логически кон-

стоенето в друг се определя по формулата:

E = P пот ∙ t zd.r.sr , [pJ]

Този параметър се използва за сравняване на различни видове логически елементи. По-добър е логическият елемент, който има по-малко този параметър.

1.3.4 Основен елемент на схемата TTL

1.3.5 Основен елемент на схемата CMOS

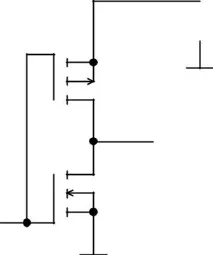

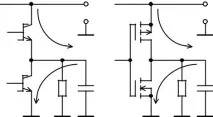

Основата на основния елемент на схемата CMOS е инвертор, базиран на еднополярни транзистори с индуцирани канали p- и (на допълващи се) , Инверторната верига (Фигура 1.18) се състои от два последователно разположени VT1 с канал и VT2 с канал.

Ако към входа на инвертора се приложи напрежение с ниско ниво U 0, тогава транзисторът VT2 е заключен и VT1 е отворен, т.е. в него се образува канал. Тъй като входният импеданс на следващия етап е много висок, напрежението на изхода на инвертора U out \u003d U 1 ≈ U p.

+

-

Фигура 1.18 - Схема на включен инвертор

При високо ниво на входно напрежение U в \u003d U 1 ≈ U p каналът се формира в транзистора VT2 и е отворен, а транзисторът VT1 е затворен и изходното напрежение

Предимства на инвертора на

- висока шумоустойчивост и в двете логически състояния (U pom ≈ 0.5U p ), тъй като входното напрежение, при което се извършва превключването, е приблизително равно на 0.5U p ;

- в статично състояние един от транзисторите няма канал за протичане на ток. Освен това, като правило, такива вериги работят върху подобни вериги, така че токът на натоварване ще бъде практически близо до нула. Следователно, в статично състояние, консумацията на енергия P pot.av ≈ 0.

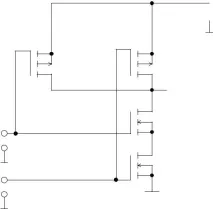

За изграждане на логически елемент с два входа са необходими два разглеждани инвертора (Фигура 1.19).

+

-

Фигура 1.19 - Включен логически елемент на смях

Логическият елемент се състои от два MOSFET с паралелно свързан канал и два MOSFET с канал, свързан последователно.Така входният сигнал управлява двойка с канали с различна проводимост, като винаги един от транзисторите ще бъде отворен, а другият затворен.

Когато и двата входа получават високо ниво на напрежение U 1, се образува канал в транзистори VT3 и VT4 и няма да има канал в сдвоени транзистори VT1 и VT2. В резултат на това ниско ниво на общата шина се предава през формираните канали към изхода на LE, т.е. U out \u003d U 0 ≈ 0.

Когато поне един от входовете получи напрежение с ниско ниво U 0, на изхода ще се появи напрежение с високо ниво, предавано от източника на захранване през канала на транзистора VT1 или VT2, т.е. U out \u003d U 1 ≈ U p.

Схемата на логическия елемент, показана на фиг.фигура 1.20.

n VT4

Фигура 1.20 - Схема на логически елемент на

Логическият елемент се състои от два MOSFET, свързани последователно с канал (VT2 и VT3) и два, свързани паралелно с канал (VT1 и VT4).

Когато поне един от входовете получи високо ниво на напрежение U 1, се образува канал в един от транзисторите, свързани паралелно (VT1 или VT4), и няма да има канал в неговия сдвоен транзистор (VT2 или VT3). След това ниско ниво на общия ши-

ny, т.е. U out \u003d U 0 ≈ 0.

Когато към двата входа се приложи ниско напрежение U 0, в транзисторите VT2 и VT3 се формират канали и напрежението на захранването се предава към изхода

ния U P, т.е. U out \u003d U 1 ≈ U P.

1.3.6 Видове изходни етапи на цифрови елементи

Цифровите елементи (логически, памет, буфер) могат да имат изходи от следните типове:

- с отворен колектор (отвод);

- с отворен излъчвател (източник).

Наличието на четири типа изходи се обяснява с различни условия на работа на елементи в логически схеми, системи и др. Изход с отворен емитер (източник) е типичен за ESL елементи (емитерна логика), които се използват за реализиране на свръхвисокоскоростни цифрови устройства. Основният им недостатък е високата енергия на превключване, поради което понастоящем ESL елементите се използват рядко. Въз основа на гореизложеното, нека разгледаме по-подробно първите три вида изходи.

Логическият изход генерира две нива на изходно напрежение: ниско ниво U 0 съответен log. 0 и високо ниво U 1 съответния дневник. 1. Изходното съпротивление на логическия изход има тенденция да бъде направено малко, за да се увеличат изходните токове, за да се увеличи скоростта на презарежданекапацитивни товари, т.е. за получаване на високоскоростен елемент. Повечето от логическите елементи, използвани в CCU, имат този тип изход.

Логическите изходни вериги на елементите на схемата TTL и CMOS са подобни на двутактните усилвателни стъпала: в тях и двата фронта на изходното напрежение се формират с участието на активни транзистори, работещи в противофаза, което осигурява ниски изходни съпротивления във всяка посока на превключване на изхода (Фигура 1.21).

Във веригата на фигура 1.21 се използват транзистори на Шотки. Това намалява енергията на превключване.

Първата характеристика на логическите изходи е, че те не могат да бъдат свързани паралелно по две причини. Това създава логически не-

сигурност, тъй като в точката на свързване на изхода, който формира дневника. 1 и изход, който генерира дневник. 0, няма да има стандартно ниво. при свързване на изходи, които са в различни логически състояния, възниква тяхната "конфронтация". Поради ниските изходни съпротивления възниква голям циркулационен ток, който може да повреди елементите на изходните вериги.