| Приоритети: | Изобретението се отнася до компютърната техника, предназначено е за сумиране на двоични числа и може да се използва в системи за предаване и обработка на информация за цифрова обработка на сигнали, при решаване на комбинаторни задачи. ЕФЕКТ: намаляване на хардуерните разходи и разширяване на функционалността поради сумиране на масиви от данни и контрол на общото количество данни с даден праг. Устройството съдържа дървовидна структура на суматори, ИЛИ елемент и компаратор, освен това информационните входове на данни на многовходния суматор се комбинират в M групи от n-битови външни входове на устройството, (M-1) n-битови суматори на дървовидната структура се комбинират в k каскади (k=]log 2 M[по-голямо цяло число), първата каскада съдържа [M/2] (цяла част) от суматори, втората каскада съдържа [M /4] суматори, , i-тата каскада съдържа [M/2 i ] суматори (i=3, 4, , k-1), , k-тото стъпало съдържа един суматор, трансферните сигнали на суматорите на етапите и изходът на компаратора, който сравнява изчислената сума на масива от входни данни с даден праг, се комбинират чрез ИЛИ и формират изходния сигнал за превишаване на прага. 1 болен.

Чертежи към патент България 2547625

Изобретението се отнася до компютърната техника, предназначено е за сумиране на двоични числа и може да бъдеизползвани в системи за предаване и обработка на информация за цифрова обработка на сигнали, при решаване на комбинаторни задачи и в контролна апаратура.

Недостатъкът на това устройство е липсата на средства за паралелно сумиране на масив от двоични данни.

Недостатъкът на това устройство е последователното сумиране на групи от едни и същи битове с натрупване на сумата в буферния регистър.

Най-близкото устройство със същата цел до заявеното изобретение по отношение на съвкупността от характеристики е броячът на броя на единиците в думата с данни (J. F. Wakerley. Проектиране на цифрови устройства. В 2 тома. - М .: Postmarket, 2002. - 1088 стр., Фиг. 6.15, стр. битови суматори и др.

Недостатъкът на това устройство е, че се извършва сумиране на едноцифрени числа.

Причините, възпрепятстващи постигането на техническия резултат, посочени по-долу, включват липсата на средства, които да осигурят сравнение на получената сума с определен праг на сумата.

Техническият резултат от изобретението е намаляване на разходите за хардуер и разширяване на функционалността чрез сумиране на масиви от данни и контролиране на общото количество данни с даден праг.

Посоченият технически резултат при изпълнението на изобретението се постига чрез факта, че елемент ИЛИ и компаратор се въвеждат в многовходния суматор, съдържащ дървовидната структура на суматорите, и информационните входове на многовходния суматор се комбинират в M групи от n-битови външни входове за данни на устройството, (M-1) n-битови суматори на дървовидната структура се комбинират в k каскади (k=]log 2 M[по-голямоцяло число), първият етап съдържа [M/2] (цяла част) от суматори, вторият етап съдържа [M/4] от суматори, , i-тият етап съдържа [M/2 i ] от суматори (i=3, 4, , k-1), , k-тият етап съдържа един суматор, външните нечетни входове за данни на устройството са свързани към първите групи от входове на съответните суматори от първия етап от суматорите, вторите групи от входове от които са свързани към външните четни групи входове за данни на устройството, информационните изходи са нечетни на суматорите на i-то стъпало (i=2, 2, , k-1) са свързани към първите групи входове на съответните суматори на (i+1)-то стъпало, вторите групи входове на които са свързани към информационните изходи на четните суматори на i-то стъпало, информационните изходи на суматора на k-то стъпало са първите изходи на устройство и са свързани към втората група входове на компаратора, чиято първа група входове е свързана към външната група входове S на устройството за максимална сума от данни, изходът на компаратора е свързан към първия вход на елемента ИЛИ, останалите входове на който са свързани към изходите на прехвърлянията на всички (M-1) суматори, а изходът на елемента ИЛИ е вторият изход на устройството.

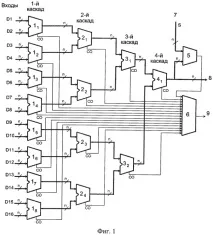

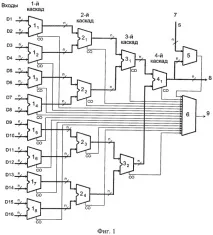

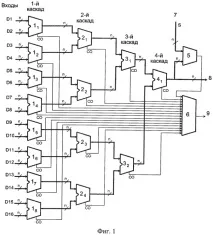

На фиг. 1 е показана схема на предлагания многовходов суматор за M=16 групи n-битови входове на устройството.

На фиг. 1 се приемат следните обозначения: суматори от първа степен 1 1 , 1 2 , , 1 8 (индексът показва номера на суматора в каскадата), суматори от втора степен 2 1 , 2 2 , 2 3 , 2 4 . суматори на трети етап 3 1 3 2 , суматор на четвърти етап 4 1 , компаратор 5, елемент ИЛИ 6, вход 7 на прага на максималната сума S, първите изходи 8 на сумата, вторият изход 9 на превишаване на зададения праг.

Многовходният суматор съдържа M групи от n-битови външни входове за данни на устройството D1-D16 (на фиг. 1 M=16). Многовходният суматор включва (M-1) n-bitсуматори, образуващи дървовидна структура, като суматорите са комбинирани в k каскади (k=]log 2 M[по-голямо цяло число). На фигура 1 броят на етапите k=4 (]log 2 l6[). Първата каскада съдържа осем суматора 1 1 , 1 2 , , 1 8 , втората каскада съдържа четири суматора 2 1 , 2 2 , 2 3 , 2 4 , третата каскада съдържа два суматора 3 1 , 3 2 , четвъртата каскада съдържа един суматор 4 1 . Външните входове на устройството D1-D16 са свързани към съответните входове на суматорите на първо стъпало 1 1 , 1 2 , , 1 8 . Изходите на суматорите на първия етап 1 1, 1 2, , 1 8 са свързани към съответните входове на суматорите на втория етап 2 1, 2 2, 2 3, 2 4, изходите на които са свързани към входовете на суматорите на третия етап 3 1, 3 2, изходите на които са свързани към входовете на суматора на четвъртия етап 4 1 .

Изходите на суматора на четвъртия етап 4 1 са първите изходи на устройството 8. Първата група входове на компаратора 5 е свързана към външната група входове 7 на устройството за максимално количество данни S, а втората група входове е свързана към изходите на суматора на четвъртия етап 4 1 .

Изходът на компаратора 5 е свързан към първия вход на елемента ИЛИ 6, останалите входове на който са свързани към изходите на трансферите С всички (M-1) суматори. Изходът на елемента ИЛИ 6 е вторият изход 9 на устройството за превишаване на предварително зададения праг S.

Предложеният многовходов суматор работи по следния начин.

Масив от входни данни се подава към M групи от n-битови външни входове на устройството D1-D16. Входните данни се добавят по двойки на суматорите на първия етап 1 1 , 1 2 , , 1 8 , на изходите на които се формират сумарни стойности и единични пренасящи сигнали CO=1, когато n-битовата сума е превишена. Освен това стойностите на сумите от първия етап се добавят към суматорите на втория етап 2 1 , 2 2 , 2 3 , 2 4 на изходите на коитостойностите на сумата и пренасящите сигнали CO=1 се генерират, когато n-битовата сума е превишена. По-нататък, сумите се изчисляват по подобен начин и се формират трансферните сигнали CO=1 за третата и четвъртата каскада.

В резултат на сумирането на изхода на суматора 4 1 на четвъртия етап ще се получи сумата от масива от входни данни, която се предава на групата от първите изходи 8. Освен това тази сума на компаратора 5 се сравнява с прага на максималната сума S, посочен на входа 7. Ако сумата на масива надвишава прага S, тогава на изхода на компа се генерира единичен сигнал ратор 5.

Единичните трансферни сигнали CO=1 на суматорите на всички и сигналът за превишаване на прага S от компаратора 5 се подават към елемента ИЛИ 6 и от неговия изход се предават към втория изход на устройството 9.

В предложеното устройство всеки от елементите на масива от входни данни D1-D16 има капацитет n. В този случай прагът на сумата S също има капацитет n. Въвеждането на проверка на трансферните сигнали на суматорите направи възможно въвеждането на един битов капацитет n за всички суматори.

Горепосочената информация ни позволява да заключим, че предлаганият многовходов суматор има дървовидна структура, има регулярна структура и връзки и съответства на заявения технически резултат - намаляване на хардуерните разходи и разширяване на функционалността чрез сумиране на масиви от данни и контролиране на общото количество данни с даден праг.

ИСК

Суматор с множество входове, съдържащ дървовидна структура от суматори, характеризиращ се с това, че в него допълнително се въвеждат елемент ИЛИ и компаратор, освен това информационните входове на суматора с множество входове се комбинират в M групи от n-битови външни входове на данни на устройството, (M-1) n-битови суматори на дървовидната структура се комбинират в k каскади (k=]log 2 M[по-голямо цяло число),първият етап съдържа [M/2] (цяла част) от суматори, вторият етап съдържа [M/4] от суматори, , i-тият етап съдържа [M/2 i ] от суматори (i=3, 4, , k-1), , k-тият етап съдържа един суматор, външните нечетни входове за данни на устройството са свързани към първите групи от входове на съответните суматори от първия етап от суматорите, вторите групи от входове на които са свързани към външни четни групи входове за данни на устройството, информационните изходи на нечетните суми на i-тото стъпало (i=l, 2, , k-1) са свързани към първите групи входове на съответните суматори на (i+1)-то стъпало, вторите групи входове на които са свързани към информационните изходи на четните суматори на i-то стъпало, информационните изходи на суматора на k-то стъпало са първите изходи на устройството и са свързани към втората група от входове на компаратора, чиято първа група от входове е свързана към външната група от входове S на устройството за максимална сума от данни, изходът на компаратора е свързан към първия входен елемент ИЛИ, останалите входове на който са свързани към изходите на прехвърлянията на всички (M-1) суматори, а изходът на елемента ИЛИ е вторият изход на устройството.