Основни параметри на логическите елементи

Основните параметри на логическите елементи включват напрежението на източника на захранване, нивата на напрежение на логическа 0 и логическа 1, капацитет на натоварване, устойчивост на шум и скорост, консумация на енергия.

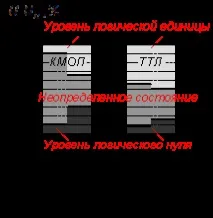

нива на журнал. 0 и лог. 1 на входа и изхода на микросхемите се различават, като правило, до 30% от напрежението на източника на захранване. В допълнение, логическите нива на CMOS микросхемите се различават значително от логическите нива на TTL микросхемите (виж фиг. 3.8). Така че, при липса на ток на натоварване, напрежението на изхода на микросхемата CMOS съвпада със захранващото напрежение (ниво log. 1) или с потенциала на общия проводник (ниво log. 0). С увеличаване на тока на натоварване, напрежението се регистрира. 1 може да бъде намален до 90%, а напрежението дневник. 0 - увеличаване до 10% на захранващото напрежение. На входа на CMOS микросхемата, минималното допустимо ниво на журнал. 1 е 70% и log. 0 - 30% от захранващото напрежение.

Товароносимост - способността на даден елемент да работи на определен брой входове на други елементи без допълнителни съвпадащи устройства се характеризира с така наречения фактор на разклоняване и се оценява от броя на единичните товари, които могат да бъдат едновременно свързани към изхода на микросхемата. Коефициентът на разклоняване на изхода за повечето логически елементи от серията TTL е 10, а за чиповете от серията CMOS е до 100.

Трябва да се отбележи, че с увеличаване на товароносимостта други параметри на микросхемите се влошават: скоростта и устойчивостта на шум намаляват, а консумацията на енергия се увеличава.

Шумоустойчивостта на основните логически елементи се оценява встатични и динамични режими. В този случай устойчивостта към статичен шум се определя от нивото на напрежението, приложено към входа на елемента спрямо нивата на логически 0 и 1, при които състоянието на изхода на веригата не се променя. За TTL елементите устойчивостта на статичен шум е най-малко 0,4 V, а за микросхемите от серия CMOS - най-малко 30% от захранващото напрежение.

Динамичната шумоустойчивост зависи от формата и амплитудата на шумовия сигнал, както и от скоростта на превключване на логическия елемент и неговата статична шумоустойчивост. Динамичните параметри на основните елементи се оценяват преди всичко от тяхната скорост. Количествено скоростта може да се характеризира с граничната работна честота, т.е. максималната честота на превключване. Максималната работна честота на съвременните TTL микросхеми е над 10 MHz, а микросхемите, базирани на CMOS структури, са само 1 MHz.

Граничната честота е ограничена от средното време на забавяне на разпространението на сигнала (виж Фиг. 3.9)

. (3.1)

Мощността, консумирана от микросхемата в статичен режим, се оказва различна на нивата на журнал. 0 (Рlog.0) и log. 1 (Рlog.1) на изхода. В тази връзка измерете средната консумация на енергия

. (3.2)

Статичната средна консумация на енергия на основните TTL елементи е няколко десетки миливата, докато на CMOS елементите е повече от хиляда пъти по-малка.

Трябва да се отбележи, че при работа в динамичен режим мощността, консумирана от логическите елементи, се увеличава. Следователно, освен консумацията на енергия в статичен режимPCP, микросхемите се характеризират и с консумацията на енергия в динамичен режимRDIN, измерена при макс.честота на превключване.

Контролни въпроси и задачи

1. Какви технологии за изграждане на логически елементи познавате?

2. Начертайте и обяснете принципа на действие на основния елемент на диодно-транзисторната логика. Посочете недостатъците, поради които диодно-транзисторната логика не се използва широко.

3. Начертайте и обяснете принципа на работа на основния елемент на NAND транзистор-транзисторната логика.

4. Начертайте и обяснете принципа на работа на основния елемент на ИЛИ-НЕ емитерно-свързана транзисторна логика. Какви са предимствата на ESL пред TTL?

5. Начертайте логически диаграми и обяснете работата на NAND и NOR елементите, реализирани върху CMOS структури.

6. Какви характеристики на приложението на CMOS чиповете знаете?

7. Избройте основните параметри на логическите елементи и ги обяснете.