Последователни устройства - страница 2

c- щифтове K561TM2; d- таблица на функциониране K561TM2

На базата на двустепенен JK тригер може да бъде изграден D тригер, както е показано на фиг. 14.

Ориз. 14 Използване на JK тригер като D тригер

a - схема за формиране на D-вход

b- чип K155TV1 (7472)

За разлика от резето, такъв D-тригер ще бъде непрозрачен за D-входа. При него отсъства феноменът на улавянето и пробива, т.к. спусъкът е с превключване.

Разглежданите тригери са комбинирани в схеми, които могат да изпълняват по-сложни задачи от един тригер. Най-известните и използвани са регистрите и броячите.

За запаметяване и преобразуване на многобитови думи, необходимият брой тригери се комбинират в една функционална единица-регистър. Регистрите, изградени върху ключалки, например K155TM5, K155TM7, K561TM3 и др., Могат да се разглеждат като четирибитови ключалки с информационни входове Di, вход за запис на сигнал - C, вход за заглушаване - R, тригерни изходи Qi. Въвеждането на информация в регистър се нарича операция за въвеждане или запис, а извличането й от регистър се нарича изход или четене. Важно обстоятелство е възможността за записване на нова информация в регистъра без предварителното й нулиране.

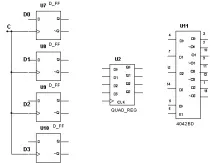

На фиг. 15 показва диаграма на регистър на паметта, предназначен да съхранява малка двоична информация. Регистърът се състои от набор от синхронни тригери, всеки от които съхранява един бит от двоично число. Въвеждането (записването) и извеждането (четенето) на информация се извършва от паралелен код. Входът се осигурява от тактов импулс, с пристигането на следващия тактов импулс, записаната информация се актуализира. Четенето се извършва в директен или обратен код (от обратенизходи).

Ориз. 15 Регистър на паметта

b- четирибитов регистър от библиотеката MISC;

v-register K561TM3 (CD4042)

Характеристика на регистъра K561TM3 е наличието на вход за превключване на полярността - POLAVITY (щифт 6 на фиг. 15c). Ако този вход E1 е нисък, информацията от входа Di ще се появи на изхода Qi по време на ниското ниво на импулса на тактовия вход - CLOCK (пин 5 на фиг. 15в). В табл. 5 показва управляващите сигнали за този регистър.

K561TM3 контролна таблица 5

Shift регистрите, в допълнение към операцията за съхранение, преобразуват серийния двоичен код в паралелен и паралелния в сериен; те извършват аритметични и логически операции, служат като елементи за забавяне на времето.

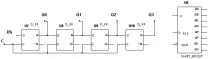

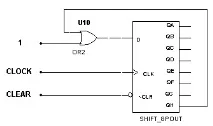

Схемата на регистъра за смяна е показана на фиг. 16.

Ориз. 16 Shift регистър

а - схема на четирибитов регистър;

b- осембитов регистър за смяна от библиотеката MISC

С пристигането на всеки тактов импулс, съдържанието на тригера на всеки бит се пренаписва (измества) към следващия бит, без да се променя редът на единици и нули. В домашните схеми буквите RG служат като регистрационен символ, а стрелката показва посоката на изместване: изместване на информацията наляво от по-ниските цифри към по-старите, изместване на информацията надясно, символът на обратен (двупосочен) регистър.

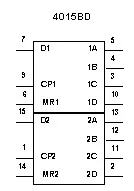

Като пример, на фиг. 17 показва параметрите на регистъра CD4015, който съответства на домашния аналог K561IR2.

Без промяна на Qn

Ориз. 17 Чип регистър K561IR2

a - библиотечно изображение 4015BD;

б- таблица на състоянието

Както се вижда от фиг. 17а, чипът K561IR2 (CD4015) съдържа два независими четирибитови регистъра за преместване. Всекирегистърът има четири изхода Q от всеки тригер (1A-1D и 2A-2D). Всички регистърни тригери са двустепенни D-тип. Данните се въвеждат в регистъра през сериен порт D (D1 и D2). Регистърът има clock-CP вход, където данните се получават от вход D на първия тригер и се изместват с една стъпка наляво (от по-ниско към високо) след всеки положителен фронт на тактовия сигнал на CP входа. Можете да нулирате регистриращите тригери, като приложите напрежение с високо логическо ниво към асинхронния вход за нулиране MR.

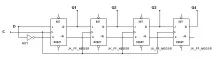

На фиг. 18 показва диаграма на преместващ регистър, образуван от JK тригери. Схемата за формиране на D-тригерната функция е показана на фиг. 14а.

Ориз. 18 Shift регистър на JK джапанки

Използването на сменителни регистри е разнообразно. В двоичната аритметика преместването на число с един бит наляво съответства на умножаването му по 2, преместването надясно съответства на разделянето му наполовина. Регистър за преместване, съдържащ само една единица, може да действа като брояч, който показва броя на сигналите, получени на входа, чрез позицията на единица в линейна скала. Ако импулси от тактов генератор се приложат към входа за смяна, тогава импулсите, генерирани на неговите изходи, могат да се използват за многофазно управление, например стъпков двигател или многофазна синхронизация.

На фиг. 19 показва диаграма на пръстеновиден разпределител на импулси, базиран на регистър за изместване.

Ориз. 19 пръстен разпределител на импулси

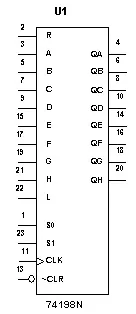

На фиг. 20 показва универсален, осем-битов, синхронен преместващ регистър K155IR13 (74198). Входовете A-H са предназначени за предоставяне на информация по време на паралелен запис, R и L (дясно и ляво) за предоставяне на информация по време на последователен запис и изместване съответно надясно и наляво, S0 и S1 за управление на режима, CLK (Часовник) за подаване на тактови импулси, CLR (Изчистване)за нулиране на тригерите на регистъра и този вход има най-висок приоритет, защото. когато се приложи 0, всички тригери се нулират независимо от състоянието на другите входове.

1

1

1

1

1

1

Ориз. 20 регистър K155IR13 (74198)

a - pinout на микросхемата;

в- функционираща маса

Друго устройство, което комбинира няколко задействания, е брояч. Както вече беше показано, регистърът за смяна може да се разглежда като функция на брояча, например броячът на Джонсън по своята структура не е нищо повече от регистър за смяна.

Броячът е устройство, чиито изходни сигнали отразяват броя на импулсите, получени на входа за броене. Когато входните сигнали пристигнат, броячът последователно изброява своите състояния в реда, определен за тази верига. Дължината на списъка с използвани състояния се нарича единица за преизчисляване или капацитет на брояча.

Различните схеми на броячи могат да итерират своите състояния в различен ред. Има: двоично кодиране, когато редът на промяна на състоянията на задействане съответства на последователност от двоични числа, единично кодиране, когато състоянието на брояча е представено от местоположението на единична единица (например регистър за смяна с една движеща се единица), единично кодиране, когато състоянието е представено от броя на единиците (например брояч на Джонсън) и по-сложни видове кодиране.

По посока на сметката са известни сумиране, изваждане и обръщане, а по метода на организиране на вътрешни връзки - с пряка връзка, със сериен път на предаване, с паралелен трансфер, комбиниран и пръстен.

Следните индикатори за време също принадлежат към класификационните характеристики на измервателните уреди: Traz.sch. резолюция -минималното време между два входни сигнала, през което няма неизправности (реципрочната стойност на Fmax. = 1 \ Tr. count се нарича максимална честота на броене), времето за настройка на Tust кода. - равно на времето между момента на получаване на входния сигнал и преминаването на брояча в ново стабилно състояние. Тези параметри зависят от скоростта на тригерите и начина, по който са свързани един с друг.

Класификационните характеристики са независими и могат да се срещат в различни комбинации.

Микросхемите на брояча се произвеждат като част от редица серии, като правило, в пакети с 14 или 16 пина, четири тригера на пакет и са добре адаптирани за увеличаване на капацитета.

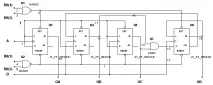

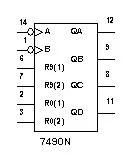

Променяйки връзките между тригерите, предприятията произвеждат броячи с различни модули за преобразуване, например 6,10,12. В някои серии TTL броячът е разделен на две части: тригер (т.е. брояч на 2), с премахнати вход и изход, и брояч на 8, 6 или 5, също със собствен вход и изход. В резултат на това един и същ чип може да се използва като брояч с няколко фактора за броене. Типичен представител на това семейство е броячът K155IE2 (SN 7490) - четирицифрен десетичен асинхронен брояч на пулсации, показан на фиг. 21. Състои се от делители на 2 и на 5, направени на тактови JK джапанки. И за двата тактови входа ръбът на тригера е преход от 0 към 1.

Ориз. 21 Структурата на брояча K155IE2

R9(1) , R9(2) – предварително заредени входове към кодов брояч 10012=910

R0(1), R0(2) - входове за синхронно нулиране

A – тактов вход на първо стъпало Ksch.=2

B – тактов вход на второ стъпало Ksch.=5

QA - тригерен изход на първия етап на брояча

QB, QC, QD - тригерни изходи на вторияконтра стъпки

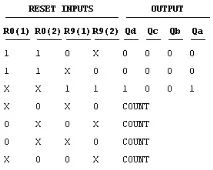

На фиг. 22 показва символа на микросхемата и таблицата на работа.

Ориз. 22 чипа K155IE2 (SN 7490)

a – таблица за избор на режим на работа

b - pinout на микросхемата

На фиг. 23 показва възможни начини за промяна на коефициента на броене на чипа K155IE2 без използване на външни допълнителни логически елементи.

Ориз. 23 Диаграми на външни връзки при промяна на фактора на броене

Формирането на липсващите коефициенти: 2, 5 и 10 е очевидно и не изисква обяснение.

В табл. 6 показва функционалното предназначение и съответствието между най-популярните местни и чуждестранни серии TTL и CMOS броячи чипове.

Съответствие на имената на чужди и местни микросхеми