Архитектура AMD Bulldozer

AMD реши да предприеме напълно различен подход с новата архитектура Bulldozer. Беше решено да се създадат двуядрени модули, които споделят някои ресурси (L2 кеш, модул с плаваща запетая), но не са напълно независими един от друг. (Вижте снимката по-долу) Според AMD това е направено с цел оптимизиране на процесора и същевременно намаляване на цената на процесора. Оптимизацията се крие във факта, че при конвенционалните многоядрени процесори някои модули може да не работят и такива модули могат да бъдат комбинирани в архитектурата Bulldozer. И ако има по-малко модули, това означава, че ще се изразходва по-малко материал, а това от своя страна ще повлияе положително на разходите, ще спести енергия и ще намали количеството топлина. Така че докато AMD ще нарича своите нови процесори с архитектура Bulldozer като двуядрени, те всъщност няма да бъдат наистина двуядрени, тъй като няма да имат напълно независими ядра. И името "двуядрен процесор " ще се използва за маркетингови цели.

За да създаде "четириядрени процесори ", AMD използва два от тези блокове, така че процесорът всъщност има два "процесора" вътре (двата градивни блока са показани на фигурата по-долу), а не четири. AMD ще продължи да нарича новите процесори четириядрени.

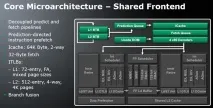

Сега нека разгледаме по-подробно модулите Fetch и Decode, използвани в архитектурата на Bulldozer.

Извличане и декодиране на модули

Модулът Fetch Fetch е отговорен за получаване на инструкции за декодиране от кеша или основната памет.

Модули за извличане и декодиране.

Както вече беше отбелязано,модулите за вземане на проби използват две "ядра" наведнъж. L1 кешът за инструкции също се използва от две ядра едновременно, но всяко ядро на процесора има собствен L1 кеш за данни. AMD вече обяви, че кешът за инструкции L1, използван в архитектурата на Bulldozer, се състои от 64K двуканален мултиасоциативен кеш. Същата конфигурация се използва в процесорите с архитектура AMD64, но с тази разлика, че процесорите AMD64 имат L1 кеш на ядро, докато процесорите Bulldozer ще имат един L1 кеш на двойка ядра. Кешът за данни обаче ще има само 16 KB, което е значително по-малко от 64 KB на ядро, използвани в процесорите, базирани на архитектурата AMD64.

Компютърните програми се пишат с помощта на x86 инструкции, но в момента процесорите разбират само собствените си RISC инструкции. Модулът за декодиране е отговорен за преобразуването на x86 програмни инструкции в RISC микроинструкции. Архитектурата Bulldozer има четири декодера, но в момента AMD не разкрива какви инструкции изпълнява всеки декодер. Обикновено един от тези декодери изпълнява сложни сложни инструкции, използвайки предоставения ROM микрокод („µкод“ или „микрокод“). Декодирането на сложни инструкции завършва след няколко цикъла, след което те се преобразуват в няколко микроинструкции. Обикновено производителите оптимизират своите процесори по такъв начин, че при декодиране на най-често срещаните инструкции те се изпълняват само в един цикъл.