Изследване на асинхронни схеми в ModelSim

Отначало четох и нищо не разбрах, после го прочетох отново и пак нищо не разбрах. Всъщност вече прочетох всички статии на ajrec за асинхронни вериги и трябва да призная, че имам малко разбиране за това какво е като цяло (въпреки че вярвам, че имам опит в проектирането на FPGA).

Честно казано, винаги гледам с любопитство проекти, които „не са като всички останали“. Вярвам, че само такива проекти имат шанс или да се провалят дълбоко, или да летят високо. Ако правите нещо по същия начин като стотици други разработчици, тогава вървите по утъпкания път, тук е лесно и удобно. Не всеки може да направи крачка встрани и да тръгне по своя път.

Опитах се да разбера проекта за асинхронен декодер и поне да направя временна симулация на кода в ModelSim. Повече за това какво излезе от него.

Честно казано, казаното в статията „Асинхронен декодер“ и „Система за синтез на самосинхронна верига Petrify: проблеми и тяхното решение“ не ми пасва добре на главата. Фундаментално съм „повреден от техниката на синхронен дизайн“.

Освен това в статията има странности, които болят окото. Например, ето един цитат:

Изходни сигнали: q1 - превключва, ако r1=1 и r2=1; q2 - превключва, ако r1=1 и r2=0; q3 - превключва, ако r1=0 и r2=1; q4 - превключва, ако r1=0 и r2=0.

Сигурно се заяждам, но трудно мога да си представя програмист, който записва номерацията на сигналите, започвайки от единица и така че q4 да превключва, когато r1=0 и r2=0. В главата ми всичко е строго според шаблона: < 0, 0 > - съответства на сигнала q0. < 0, 1 > - съответства на сигнала q1. < 1, 0 >- съответства на сигнала q2 и < 1, 1> - съответства на сигнал q3. Но това, разбира се, са дреболии, които не са от значение.

Всъщност това име подтикна да опитам да симулирам логиката на декодера, описан от ajrec. Времевата симулация е достатъчно добър модел, който ще покаже поведението на веригата в реална FPGA. Вярно... тук има едно предупреждение - не съм напълно сигурен, че ModelSim ще може надеждно да симулира асинхронни вериги: симулаторът ModelSim е предназначен предимно за "традиционен" синхронен дизайн.

Така. Изходният код от статията FPGA / Asynchronous decoder не знаем на какъв език и изглежда така:

e=НЕ(o1); e1=И(o1,j1); e2=И(o2,h1); e3=NAND(e,i1); e4=OR(o2,h1); f1=И(d,r1); f2=И(d,r2); g=НЕ(d); h1=NOR(g,r1); h2=NOR(g,r2); i1=ИЛИ(f1,j1); i2=ИЛИ(f2,j2); j1=NOR(g,i1); j2=NOR(g,i2); k1=И(e1,j2); k2=И(e1,h2); k3=И(e2,j2); k4=И(e2,h2); l1=И(t1,i2); l2=ИЛИ(t2,h2); l3=И(t3,i2); l4=ИЛИ(t4,h2); m1=ИЛИ(k1,n1); m2=ИЛИ(k2,n2); m3=NOR(k3,n3); m4=ИЛИ(k4,n4); n1=ИЛИ(l1,m1); n2=NOR(l2,m2); n3=NOR(l3,m3); n4=NOR(l4,m4); o1=NOR(p1,p2); o2=NOR(p3,p4); p1=NOR(m1,s1); p2=NOR(m2,s2); p3=NOR(m3,s3); p4=NOR(m4,s4); s1=NOR(n1,l1); s2=NOR(n2,l2); s3=NOR(n3,l3); s4=NOR(n4,l4); t1=NOR(e3,s1); t2=ИЛИ(e3,s2); t3=NOR(e4,s3); t4=ИЛИ(e4,s4); q1=NOR(s1,k1); q2=NOR(s2,k2); q3=NOR(s3,k3); q4=ИЛИ(s4,k4).

По-нататък в статията има еквивалентна схема на това нещо и се казва, че като цяло сигналите m1, m2, m3, m4 все още трябва да бъдат върнати в първоначалното си състояние, преди да започнат работа. Добре, ще пренапиша всичко във Verilog така:

Опитах се да направя минимални промени в изходния код, за да не наруша случайно логиката, която не разбирам. Така че дефинирах функциите на Verilog AND, OR, NOR, NAND да правят това, което трябва да правят. Присвояването на стойност на сигнала във Verilog се извършва чрез assign. Ако някойнужда, тогава ето кратко описание на езика Verilog.

В допълнение, добавих gag, четири-битов изходен сигнал qq, който се изчислява от традиционен декодер, както следва: assign qq = 1 Settings => EDA Tools Settings=> Симулация, изберете Име на инструмент => Модел Sim-Altera. След това, след компилация, ще бъде създадена папка simulation/modelsim, която ще съдържа *.sdo и *.vo модулите, които са необходими за временна симулация.

Сега имаме нужда от тестова стенда. Написах го по прост начин:

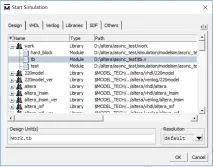

Сега използвам ModelSim-Altera (или сега Intel). Създавам проект и работно пространство. Добавям два съществуващи файла към него: tb.v testbench и проекта async_test.vo, компилиран от Quartus:

Сега те все още трябва да бъдат компилирани с помощта на ModelSim. Щракнете с десния бутон и изберете Compile All от менюто. Необходимо е до всеки файл да има зелени отметки. Понякога има странност и ModelSim намира синтактични грешки там, където quartus не ги вижда. Това е така, между другото.

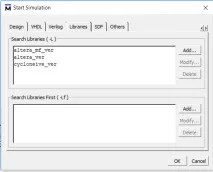

Вече можете да започнете симулация чрез менюто ModelSim, Simulate-> Стартиране на симулация... Тук се появява диалогов прозорец, където трябва:

1) изберете горния модул и сега това е тестова стенда

2) добавете алтера библиотеките

3) добавете компилиран SDF файл, от който ще излязат всички временни параметри

След успешното зареждане на всички файлове и модули, необходими за симулацията, трябва да добавим интересуващите ни сигнали в прозореца на времевата диаграма.

Щракнете върху OK и след това менюто Simulate => run=> Изпълнение на всички

Това е - проработи!

Втората група от 4 импулса d не работи правилно. Това е моментът, в който сигналът d пристига едновременно с промяната на r1 и r2.

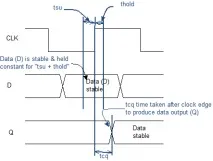

Тук бих искал да бъда по-точен.разбират ролята на сигнала d. В синхронната логика знам, че има тактова честота, която заключва данните, идващи от един регистър в друг чрез комбинирани функции. В този случай разработчикът трябва да предостави така наречените времеви параметри tsu и thold. Ето и първата попаднала снимка по темата от Google:

Какво е стабилен сигнал? Има регистър, в който се съхраняват входните данни. Следва логическа функция, която от входните данни (може да са няколко цифри) изчислява следващата стойност, която се съхранява в следващия регистър. Така че логическата функция трябва да изчисли резултата за време, по-малко от продължителността на тактовия период. Не само за да има време за изчисляване. Тъй като има няколко бита, резултатът все още трябва да има време да премине по протежение на проводниците, всеки към своя собствен регистър на ключалката.

Сега, връщайки се към асинхронната верига и сигнал d, разбирам, че втората група от четири импулса d в тази асинхронна верига по време на симулацията не изглежда да работи правилно поради точно същата причина, поради която синхронната верига може да не работи. А именно цу не се издържа. Сигналът d пристига, когато сигналите r1 и r2 все още не са пристигнали или не са стабилни.

Друга мисъл не ме напуска.

Струва ми се, че традиционен декодер като този, който имам по-горе, присвоява qq = 1 Етикети:

- FPGA

- асинхронни вериги

- ModelSim

- Verilog

И тук можемполучавате грант за пробен период на Yandex.Cloud. Необходимо е само да въведете "Habr" в полето "секретна парола".