Логически елементи на интегрални схеми

БЕЛОБЪЛГАРСКИ ДЪРЖАВЕН УНИВЕРСИТЕТ ПО ИНФОРМАТИКА И РАДИОЕЛЕКТРОНИКА

"Логически елементи на интегрални схеми"

Най-често срещаните са схемите LE и потенциален тип. Сред съществуващите логически елементи (потенциални, импулсни, импулсно-потенциални), потенциалните LE и вериги представляват най-често срещания клас. Основната отличителна черта на схемите LE и потенциален тип от импулсни и импулсно-потенциални е наличието на връзка с постоянен ток между техните входове и изходи. Друга отличителна черта е, че те могат да бъдат контролирани и управлявани от други вериги, използвайки сигнали с ограничена (импулсни сигнали) и неограничена (потенциални сигнали) продължителност.

В общия случай не се изключва възможността за използване на реактивни компоненти в такива вериги, т.е. индуктивности и капацитети. Последните обикновено играят поддържаща роля. Въпреки това фундаменталната възможност за изграждане на ИС с различна сложност без реактивни компоненти е това, което отличава този клас устройства от останалите, тъй като техният производствен процес отговаря най-добре на възможностите на микроелектронната технология.

Степента на интеграция на ИС от потенциален тип и сложността на техните функции непрекъснато нарастват. Електрическата реализация на IC от потенциален тип се извършва на базата на редица стандартни, основни функционални елементи.

Параметрите, характеризиращи логическите и схемните възможности на микросхемите LE и големите интегрални схеми (LSI), включват:

1. реализируема логическа функция;

2. капацитет на натоварване n, който характеризира възможността за свързване на определен брой идентични електропроводи(коефициент на разклоняване на изхода);

3. коефициент на агрегиране на изхода m (mi - за изпълнение на логическата функция И; mior - за изпълнение на логическата функция ИЛИ) (комбинационен коефициент за входа);

4. средно забавяне на предаване на сигнала τav (половината от сумата на времезакъсненията за предаване на сигнали 1 и 0 от входа на LE към изхода му);

5. пределна работна честота fr (честота на превключване на тригера, съставен от разглеждания LE);

7. консумация на енергия.

Според вида на реализираната логическа функция LEможе условно да се раздели на два класа. Първият клас включва функционални елементиедностепенналогика. Това са най-простите LE, които имплементират функциите И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ. Вторият клас включва функционални елементина двустепенналогика, които реализират по-сложни функции: И-ИЛИ, ИЛИ-И, НЕ-ИЛИ, И-ИЛИ-НЕ, И-ИЛИ-И и др.

ТовароносимостLE n определя броя на входовете на еднакви елементи, които могат да бъдат свързани към изхода на всеки от тях. Това осигурява неизкривено предаване на двоични символи 0 и 1 в цифрово устройство по верига от произволен брой последователно свързани елементи с най-лошите комбинации от дестабилизиращи фактори. Дестабилизиращи фактори могат да бъдат: промяна в захранващите напрежения, разминаване в параметрите на компонентите, промяна в температурата и др.

Често товароносимостта n се наричакоефициент на разделяне на изхода(Kraz ) и се изразява като положително цяло число (n=4, 5, 7, 10 и т.н.).

Колкото по-висока е товароносимостта на LE, толкова по-широки са техните логически възможности и толкова по-ниски са разходите за проектиране и изграждане на цифрово устройство. Възможно е обаче увеличение на параметъра n до определени граници, тъй като това се влошавадруги параметри на LE: скоростта намалява, шумоустойчивостта се влошава и консумацията на енергия се увеличава. Обикновено една серия ИС често включва ЛЕ с различна товароносимост: главни ЛЕ с n=4...10 и буферни елементи - така наречените усилватели на мощност с n=20...50. Това позволява по-гъвкаво проектиране на цифрови устройства, постигайки оптимална производителност по отношение на консумацията на енергия и броя на LE.

В зависимост от честотния диапазон на работа на логическите MIS микросхеми (метал-диелектрик-полупроводник), тяхната товароносимост може да варира в широк диапазон (n=10…100).

Коефициентът на комбиниране по входm(Kob ) характеризира максималния брой логически входове на функционалния елемент. С увеличаване на параметъра m, логическите възможности на микросхемата се разширяват поради изпълнението на функции с голям брой аргументи на един типичен елемент И-НЕ, ИЛИ-НЕ и т.н. Въпреки това, с увеличаване на броя на входовете, като правило, други параметри на функционалния елемент се влошават, като скорост, устойчивост на шум и капацитет на натоварване.

От гледна точка на възможността за увеличаване на коефициента на комбинация на входа И или на входа ИЛИ, логическите схеми се различават значително една от друга. Например, в IC, където функцията на първия логически етап се изпълнява върху диоди или емитерни преходи на транзистор с множество емитери, увеличаването на броя на входовете не изисква значителни допълнителни разходи за кристалната площ. В интегралните схеми, където функцията на първия логически етап се изпълнява на транзистори, увеличаването на параметъра m изисква значително увеличаване на броя на LE компонентите и увеличаване на площта на IC чипа.

В съществуващите серии от интегрални схеми основните логически елементи обикновено се правят с малък брой входове.

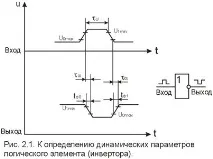

ДА СЕосновнитединамични параметрина логическия елемент са:

tf1 - предната част на формирането на нивото на логическа 1;

tf0 - фронтът на формирането на нивото на логическата 0;

τ10 е забавянето на превключването от състояние 1 към състояние 0;

τ01 е забавянето на превключването от състояние 0 към състояние 1;

fp е работната честота.

Определянето на тези параметри се осигурява чрез сравняване на сигналите на входа и изхода на LE, т.е. когато се разглежда процесът на предаване на информация чрез LE.

На фиг. 1 са показани характеристиките на сигналите на входа и изхода на инвертора и са показани отчетните нива, спрямо които се определят динамичните параметри на ЛЕ.

Ориз. 1. Да се определят динамичните параметри на логически елемент (инвертор)

Референтните нива на динамичните параметри на LE са (разглежда се положителна логика, при която високото ниво на изходния сигнал съответства на 1, а ниското ниво на 0) максималното ниво на логика 0 и минималното ниво на логика 1. Закъснението на превключване τ10 се определя като времевия интервал между ниво 1 на нарастващия фронт на входния импулс (положителен импулс) и ниво 0 на падащия фронт на изходния импулс (отрицателен импулс ).

Закъснението при превключване τ01 се определя като времевия интервал между ниво 0 на спадащия фронт на входния импулс и ниво 1 на нарастващия фронт на изходния импулс.

Фронтовете на импулса, определени между нива 1 и 0 на затихване на импулса, се обозначават tf0, между нива 0 и 1 на нарастване на импулса - tf1.

Средното закъснение τav LE се определя като половината от сумата на закъсненията τ10 и τ01 и служи като среден параметърпроизводителност, използван при изчисляване на времевите характеристики на многоелементни последователно свързани логически схеми.

работасредното забавяне на брой LE, свързани последователно в устройството, дава най-голямото забавяне на сигнала в това устройство. Параметърът τav е даден в техническите спецификации на ИС. За да се опрости процеса на изчисляване на времевите характеристики на сложни логически схеми, сигналите често се считат за правоъгълни, т.е. tf0 = tf1 =0.

Устойчивост на шум.Основният елемент на ИС в статичен режим може да бъде в едно от двете стабилни състояния (0 или 1). Поради тази причина устойчивостта на статичен шум на LE се отличава с ниво 0 (Uno) и ниво 1 (Un 1). Устойчивостта на статични шумове на основните елементи на ИС се определя от стойността на напрежението, което може да бъде приложено към входа на ИС спрямо ниво 0 или 1, без да предизвика фалшивото му сработване (например преход от състояние 1 към състояние 0 или обратно).

Напрежението на смущение повишава или понижава входното напрежение. Ако на входа се приложи логическо 0 напрежение (U0), тогава смущенията с положителна полярност са опасни, тъй като те повишават входното напрежение, което може да доведе до неизправност, т.е. фалшива промяна на изходните напрежения в цифрово устройство. Когато към входа са приложени напрежение логическа 1 (U1) и напрежение на смущение с отрицателна полярност, също е възможно фалшиво превключване. Максимално допустимите директни напрежения на смущения с положителна полярност (при логическо 0 напрежение на входа) и отрицателна полярност (при логическо 1 напрежение на входа) определят шумовата устойчивост на LE по отношение на статични (дългодействащи) смущения.

Вътрешни смущения в цифрово устройство възникват при превключване на LE, следователно тяхната амплитуда е пропорционална на логическата разлика Ul.

Логически спаде разликата в напрежението между логика 1 и логика 0:

ЗаОценките за устойчивост на шум LE, в допълнение към напреженията Up1 и Up0, използват относителни стойности: