Паралелни ADC (флаш ADC)

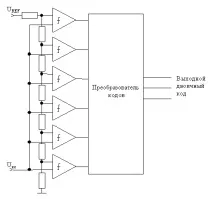

Най-простият в разбирането на принципите на работа (но в никакъв случай не по отношение на вътрешната структура) е паралелен аналогово-цифров преобразувател (flash ADC). Помислете за неговата работа, като използвате примера на трибитова паралелна ADC верига, показана на фигура 1.

При тази схема аналоговият сигналUin се подава към съответния вход на АЦП. В същото време референтното напрежениеUREFсе прилага към другия му вход. Това напрежение се разделя на седем равни нива с помощта на резистивен делител, състоящ се от резистори с еднакво съпротивление.

В сърцето на паралелния аналогово-цифров преобразувател са седем аналогови компаратора, които сравняват входния сигнал на ADC с референтно напрежение, приложено към техния втори вход. Ако напрежението на входа на компаратора превишава напрежението на инвертиращия му вход, тогава на изхода на компаратора се формира напрежението на логическата единица. Аналоговите компаратори са вътрешно много подобни на операционните усилватели с диференциален вход. Разликата е наличието на цифрово изходно стъпало (с TTL или ESL логически нива).

Ако напрежението на входа на аналогово-цифровия преобразувател е по-малко от всички напрежения, приложени към референтните (инвертиращи) входове на компараторите, тогава на всички изходи на компараторите се формират нулеви нива на сигнала. Кодът на изхода на линията за сравнение ще бъде равен на 0000000b.

Постепенното увеличаване на нивото на входния сигнал може да надвиши напрежението на референтния вход на долния компаратор. В този случай на неговия изход ще се формира ниво на логическа единица. Кодът на изхода на линията за сравнение ще приеме стойността 0000001. С по-нататъшно увеличаване на нивото на сигнала на входа на паралелния ADC, кодът ще вземестойности 0000011, 0000111 и т.н. Максималната кодова стойност 1111111 ще бъде издадена на изхода на линията от компаратори на паралелния аналогово-цифров преобразувател, когато входният сигнал надвиши стойността на сигнала на еталонния вход на най-високия компаратор.

И така, достигнахме пълния мащаб на напрежението на аналогово-цифровия преобразувател (ADC). Въпреки това, както забелязахте, кодът, получен на изхода на линията за сравнение, се състои от нули и единици, но не е двоичен в същото време, следователно, за да го преобразувате в двоична форма, ще ви е необходима специална цифрова схема - преобразувател на кодове (енкодер).

Ние вече знаем как да разработваме такива схеми. Това научихме в първата част на курса "Цифрови устройства и микропроцесори". Ако внимателно разгледаме кодовете, които получихме на изхода на линията от компаратори, ще видим, че вече сме се срещали с този тип кодове - това са кодовете, които използвахме при изграждането на осмични енкодери. А това от своя страна означава, че можем да използваме вече добре познатата осмична енкодерна схема като конвертор на кодове.

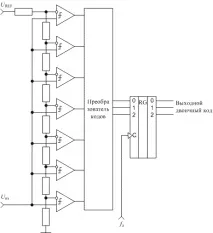

Сега нека си припомним, че готовият преобразуван двоичен код трябва да бъде доставен на изхода на аналогово-цифров преобразувател с честота на дискретизация. Можем да гарантираме това, като съхраним кода, идващ от изхода на приоритетния енкодер, в паралелен регистър, както е показано на фигура 2.

Максималната тактова честота, приложена към входа за синхронизация на паралелния ADC, се определя от разликата в разпространението на сигнала. В същото време трябва да се отбележи, че при производството на компаратори на един чип, разпространението на техните параметри, включително времето за разпространение на сигнала от неговиявход към изход ще бъде много по-малко от абсолютната стойност на закъснението. Когато компараторите са свързани паралелно, разликата в разпространението на сигнала на техните изходи обикновено не надвишава 10 ps. Следователно максималната тактова честота, която е и максималната честота на дискретизация на аналогов сигнал, достига стойност от 500 MHz. Примерите включват аналогово-цифрови преобразуватели ADC08D1000 от National Products от Texas Instruments, AD9484 или AD9434 от Analog Devices.

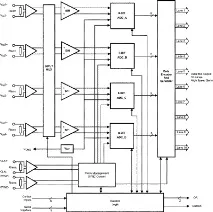

Някои приложения, като цифрови осцилоскопи или радиоприемници, може да изискват дори по-високи честоти на дискретизация за аналогов входен сигнал. Тогава се използва паралелно свързване на няколко паралелни АЦП. За предаване на изходните цифровизирани кодове се използват и няколко паралелни шини за данни. Пример за това е чипът LM97600 от Texas Instruments. Вътрешната му структура е показана на фигура 3.

- Микушин А.В., Сажнев А.М., Сединин В.И. Цифрови устройства и микропроцесори. Санкт Петербург, BHV-Петербург, 2010 г.

- Федорков Б. Г., Телец В. А. DAC и ADC микросхеми: функциониране, параметри, приложение - М., Енергоатомиздат, 1990. - 320 с.

- Високопроизводителен, нискоенергиен, 8-битов, 2,5 GHz ADC

- LM97600

Заедно със статията "Паралелни АЦП (флаш АЦП)" те гласят: