Харвардска архитектура

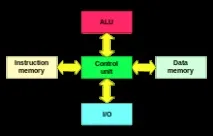

Харвардска архитектура- компютърна архитектура, отличителните черти на която са:

- хранилището на инструкции и хранилището на данни са различни физически устройства;

- каналът за инструкции и каналът за данни също са физически разделени.

Архитектурата е проектирана от Хауърд Айкен в края на 30-те години на миналия век в Харвардския университет.

Съдържание

Харвардската архитектура е използвана от съветския учен А. И. Китов в Изчислителния център-1 на Министерството на отбраната на СССР [3] .

Типичните операции (събиране и умножение) изискват няколко действия от всяко изчислително устройство:

Идеята, реализирана от Aiken, е да се разделят физически линиите за командване и предаване на данни. Първият компютър Mark I на Aiken използва перфорирана лента за съхраняване на инструкции и електромеханични регистри за манипулиране на данни. Това направи възможно едновременното изпращане и обработка на команди и данни, което значително увеличи общата скорост на компютъра.

Разлика от фон Ноймановата архитектура

В компютър, използващ архитектурата на Харвард, процесорът може да прочете следващата инструкция и да работи с паметта за данни едновременно и без да използва кеш паметта. По този начин, компютър с архитектура на Харвард, с определена сложност на схемата, е по-бърз от компютър с архитектура на фон Нойман, тъй като инструкциите и потоците от данни са разположени на отделни хардуерни канали, които не са физически свързани един с друг.

Модифицирана архитектура на Харвард

Такава схема се използва в съвременните сигнални процесори. Те отидоха още по-далеч по пътя на намаляване на разходите при създаването на едночипови микрокомпютри - микроконтролери. При тях се използва една шина от команди и данни вътре в кристала.

Разделянето на шините в модифицираната структура на Харвард се извършва с помощта на отделни контролни сигнали: четене, запис или избор на област от паметта.

Разширена Харвардска архитектура

Често е необходимо да се изберат три компонента: два операнда и инструкция (в алгоритмите за цифрова обработка на сигнали това е най-честата задача при FFT, FIR и IIR филтри). За това е кеша. В него може да се съхранява инструкция - следователно и двете шини остават свободни и става възможно прехвърлянето на два операнда едновременно. Използването на кеш памет заедно със споделени шини се нарича "Super Harvard Architecture" ("SHARC") - разширена архитектура на Харвард.

Процесорите на Analog Devices са пример: ADSP-21xx е модифицирана архитектура на Харвард, ADSP-21xxx (SHARC) е разширена архитектура на Харвард.

Хибридни модификации с фон Нойман архитектура

Съществуват хибридни архитектури, които съчетават предимствата както на архитектурите на Харвард, така и на фон Нойман. Съвременните CISC процесори имат отделен кеш от ниво 1 за команди и данни, което им позволява да получават както команда, така и данни за нейното изпълнение в един работен цикъл. Тоест ядрото на процесора е хардуер на Харвард, но е софтуер на фон Нойман, което опростява писането на програми. Обикновено в тези процесори една шина се използва както за предаване на команди, така и за предаване на данни, което опростява схемата на системата. Съвременните версии на такива процесори понякога могат да съдържат вградени контролери за няколко различни типа шини наведнъж за работа с различни типове памет - например DDR RAM и Flash. В този случай обаче автобусите обикновено се използват както за предаване на команди, така и за предаванеданни без разделяне, което прави тези процесори още по-близо до фон Ноймановата архитектура, като същевременно запазва предимствата на Харвардската архитектура.

Първият компютър, използващ идеята за архитектурата на Харвард, беше Mark I.

Харвардската архитектура се използва в PLC и микроконтролери, като Microchip PIC, Atmel AVR, Intel 4004, Intel 8051, както и в кеш паметта от първо ниво на x86 микропроцесори, която е разделена на два еднакви или различни блока за данни и команди.