KNOW INTUIT, Лекция, RAM

RAM като информационен буфер

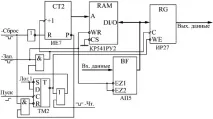

Втората най-важна употреба на RAM чипове е организирането на различни информационни буфери, тоест буферна памет за междинно съхранение на данни, прехвърлени между две устройства или системи. Същността на информационния буфер е следната: предавателното устройство записва предадените данни в буфера, а приемащото устройство чете получените данни от буфера (фиг. 12.10).

Такова междинно съхранение позволява по-добра координация на работата на устройствата, участващи в обмена на данни, повишаване на тяхната независимост едно от друго и координиране на скоростта на предаване и приемане на данни.

Нека, например, компютър действа като първо устройство, а LAN кабел като второ. Много по-удобно е компютърът да издава данни със скорост, определена от собствената му производителност, но данните трябва да се прехвърлят към локална мрежа със строго определена скорост, определена от мрежовия стандарт (например 100 Mbps). Освен това компютърът, ако е възможно, не трябва да се разсейва от наблюдение на текущото състояние на мрежата, нейната заетост и освобождаване. Следователно в този случай е необходима буферна памет. И по същия начин е необходимо при получаване на данни от локална мрежа към компютър.

Информационните буфери са еднопосочни (вход или изход) и двупосочни (т.е. вход и изход едновременно - фиг. 12.11). Например буферната памет на мрежовия адаптер е двупосочна, тъй като буферира както информацията, изпратена към мрежата от компютъра, така и информацията, получена от мрежата към компютъра. Двупосочните буфери винаги са по-трудни за проектиране поради повече потоци от данни.

Информационни буфери с периодичен режимобмените могат да бъдат организирани според типа FIFO или типа LIFO.

По този начин разнообразието от информационни буфери е огромно. Тук ще разгледаме само три примера за схеми на буферна памет.

След приключване на процедурата по записа, записващото устройство позволява четене от паметта чрез настройка на тригера на единица с положителен фронт на сигнала "Старт" (нула на инверсния изход). В този случай е разрешено преминаването на сигнал „–четв. Адресите на паметта се превключват на задния фронт на сигнала "–read", а на същия фронт данните, прочетени от паметта, се фиксират в изходния регистър, задействан от фронта (например IR27). Изходният регистър изпълнява две функции: той не предава данните, записани в паметта, към изхода (сигналът -WE забранява записа към тригера), а също така гарантира, че всички битове на прочетените данни се променят едновременно. Изходната информация поради този регистър се забавя с един период от сигнала "-Th", което трябва да се вземе предвид. Ако вземете регистър с вход за нулиране на нула, тогава можете да направите изходния код на веригата нула по време на процедурата за запис на паметта.

След края на четенето на цялото количество памет се генерира сигнал за прехвърляне на брояча -P, който отново поставя цялата верига в режим на запис, нулирайки тригера на нула (един на обратния изход). След това външното записващо устройство може да започне отново процедурата за запис на паметта.