лекции - Лекции по схемотехника - Лекция

Цифрови матрични умножители.

Матричен умножителен блок.

Блок за сумиране на умножител на матрица.

Умножение на числата с отчитане на знака.

Блок за умножение на матрица, блок за сумиране на множител, умножение със знак.

Умножението на числа в компютър се основава на последователно изместване на операндите и паралелно събиране на получените частични продукти.

Хардуерната реализация на функционални възли за умножение на числа е свързана със структурата на математически израз, който описва операцията умножение.

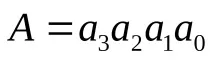

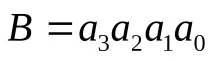

Една от опциите може да бъде представена по следния начин. Нека има две 4-битови числа

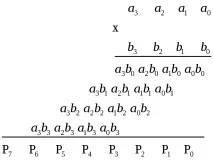

Според тази схема продуктът ще бъде равен на:

частичните продукти

Добавянето в колони се извършва в суматори. В общия случай, ако ,, тогава произведението, ако m=n, тогава общият брой елементи „И“ се определя като n 2, където k е дължината на думата, а броят на подредените суматори е n(n-1).

Структурата на матричния умножителен блок.

Веригата съдържа 16 конюнктора ("И") и 12 суматора.

Времето за сумиране определя главно скоростта на веригата, а оттам и операцията умножение.

Матричните умножители могат да бъдат просто умножителни единици (MB) или единици за добавяне на умножител (MSB).

SMB изпълнява операцията:

За операндите и са предоставени допълнителни входове.

Така че за m=4 и n=2 блоковата диаграма на блока за умножение - сумиране ... е както следва:

За умножителните блокове скоростта (максималното време за умножение) се определя от най-дългата верига за предаване на сигнала (най-десния диагонал + долния редматрици).

Тъй като долният ред на матрицата е сериен суматор за пренасяне, скоростта на MB може да се увеличи чрез замяна на последния ред с паралелен пренос SM.

Матричните умножители с голяма размерност са изградени от модули с по-малка размерност, които могат да се използват както като MB, така и като MSB.

При работа с числа със знак най-често се използва кодът на комплемента. На входа на MB са инсталирани преобразуватели на допълнителния код към директния, а на изхода на MB е инсталиран преобразувателят на директния код към допълнителния.

Кодовите конвертори се управляват от най-значимите битове на операндите (an, bn). Ако най-значимият бит е 0, тогава кодът преминава през конвертора без промяна, ако е 1, тогава той се преобразува. Ако знаците на операндите са различни, тогава произведението се преобразува в допълнение на две.

Тъй като закъсненията в преобразувателите са значителни, те могат почти да удвоят времето за изпълнение на операцията. Ако изключим конверторите и умножим числата директно в допълнителен код, тогава можем значително да увеличим скоростта на умножителните устройства.

Въпроси за контрол:

Как се умножават числата в компютър?

Как се изгражда умножителен блок?

Как се изгражда блок за сумиране на множител?

Как става умножението на числата с отчитане на знака?

Угрюмов Е.П. Проектиране на елементи и компоненти на компютър - М.; висше училище, 1987, с. 199-206.