моделиране на вериги

Урок 8

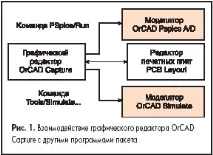

Така CAD OrCAD използва не един универсален, а два специализирани моделира. Естествено възниква въпросът кога и какво да прилагаме? За да отговорим, нека разгледаме възможните типове проекти в този пакет. На фиг. Фигура 2 показва диалоговия прозорец Нов проект, който вече познаваме. Да напомня, че се извиква с командата File/New/Project (урок 1). Можем да изберем всеки от четирите вида.

Вторият тип проект се нарича PC Board Wizard. Изглежда, че изобщо не ни подхожда, защото (съдейки по името) става въпрос за дизайна на печатни платки. Това обаче е „капан“. Този тип проекти трябва да бъдат избрани, ако ще разработваме чипове с малка и средна степен на интеграция и впоследствие да ги симулираме. Що се отнася до името, то само подчертава възможността за извършване на оформление на печатни платки след моделиране (или вместо него). Важно е да се отбележи, че в този режим имаме алтернатива: PCB PSpice или PCB Simulate проекти.

-

PSpice PCB проекти се създават, ако в диалоговия панел PCB Project Wizard (фиг. 3) поставите отметка в полето Enable project simulation и изберете горния ред: Добавяне на ресурси за симулация на аналогов или смесен сигнал. Този проект ще бъде моделиран от OrCAD PSpice A/D.

Третият тип проект - програмируема логика - ви позволява да синтезирате и симулирате прости програмируеми логически устройства. Това става с програми.OrCAD Capture и OrCAD Simulate. По-сложните проекти се изпълняват с помощта на специализирани софтуерни инструменти от производители на FPGA, като Altera, Xilinx и др. Например Altera предлага системата за проектиране Max+Plus II за тези цели [1].

Четвъртият тип проект се използва само за създаване и документиране на електрически схеми. В него не е възможно моделиране и разработка на печатни платки.

По този начин, за дигитално моделиране, изборът всъщност се стеснява до дизайни тип PCB. Помислете за технологията за проектиране и моделиране на вериги в тези режими.

-

Създайте нов проект, като напишете File/New/Project….

1.1. Въведете името му, например test_dc (декодер 2 > 4).

1.2. Посочете местоположението му на диска, например E:\OrCAD_9\dc. Ако посочената папка не съществува, тя ще бъде създадена автоматично.

1.3. Задаваме типа на проекта, в нашия случай трябва да изберем опцията: PC Board Wizard - моделиране и трасиране на печатни платки за стандартна логика на по-ниско и средно ниво на интеграция.

4.1. Поставяме елементите (команда Place / Part ...).

4.2. Свързваме ги с проводници (команда Place/Wire).

4.3. Задаваме проводниците с персонализирани имена - псевдоними (команда Place / Net Alias ...). Не забравяйте, че веригата с името трябва да бъде "облегната" на проводника, който назовавате, така че да докосва веригата.

4.4. Поставяме маркери в точките, които искаме да наблюдаваме на екрана при показване на резултатите (команда PSpice/Markers/Voltage Level).

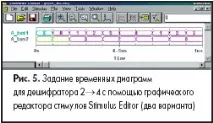

4.5. Въвеждаме генератори на външни въздействия за входни сигнали А0 и А1. Ако ги разглеждаме като елементи на двубитовата шина A[1..0], тогава ни трябва само един двубитов DigStim2 стимул (команда Place/Part, библиотека SOURCSTM). Дайте му име, например Implementation = A_bus1. По-точно, това дори не е името на стимула, а името на времевата диаграма, която той ще генерира. Използвайки командата Place/Bus, нарисувайте автобус и му дайте име A[1..0]. Към него свързваме изхода на генератора на стимул DigStim2 и проводниците A0 и A1 (фиг. 4).

Важно е да запомните, че автобусът трябва да носи същото име като имената на мрежите, включени в него. Що се отнася до атрибута Implementation, неговата стойност може да бъде произволна, но не може да бъде указана във формата на името на шината (квадратните скоби обикновено се игнорират).

Създаваме профил за симулация, например test_dc.sim, в който въвеждаме параметрите за симулация на нашия проект (команда PSpice / New Simulation Profile). Докато не създадете този файл, системата няма да ви позволи да изпълнявате команди за симулация. Вероятно не без причина последователността от команди в менюто на PSpice и иконите на лентата с инструменти е подредена в правилния ред.

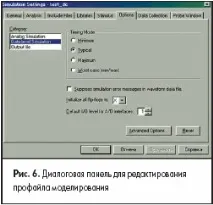

В раздела Анализ (активен по подразбиране)задайте желания тип анализ - Time Domain (Transient) и крайното време на симулация, например Run to time = 1000 ns, а в раздела Option (фиг. 6) - Gate-level Simulation метод на симулация и режим на забавяне, например Typical.

Можете да създадете повече от един симулационен профил, като test_dc_typ.sim и test_dc_max.sim, и да симулирате вашата верига при номинални или максимални закъснения. За да изберете конкретна опция, трябва да активирате съответния профил. Изберете го (фиг. 7), след което щракнете с десния бутон, за да отворите изскачащото меню и изпълнете командата Направи активен. Активният профил ще бъде маркиран с "!".

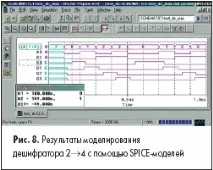

С помощта на командата PSpice/Run стартираме нашия проект за моделиране. След известно време на екрана на монитора се появява работният панел на симулатора OrCAD PSpice A/D с резултатите от симулацията (фиг. 8).

Ако сте работили с пакета DesignLab 8, то ви предстои още една среща със стария „познат“ – моделиращият постпроцесор Probe. Обаче не съвсем така. В пакета OrCAD 9 симулаторът PSpice A/D и постпроцесорът Probe (продукти на MicroSim) са обединени в една програма, която запазва старото име PSpice A/D. Потребителите, които не са запознати с тези приложения, се съветват да се обърнат към литературата [2].

-

Създайте нов проект, като напишете File/New/Project…

1.1. Въведете името му, например test_mux4 (мултиплексор 4 > 1).

1.2. Посочете местоположението му на диска, например E:\OrCAD_9\mux4. Ако посочената папка не съществува, тя ще бъде създадена автоматично.

1.3. Задайте типа на проекта (в нашия случай изберете опцията PC Board Wizard - моделиране и трасиране на печатни платки за стандартна логика на по-ниско и средно ниво на интеграция).

4.1. Поставяме елементите (команда Place / Part ...).

4.2. Свързваме ги с проводници (команда Place/Wire).

4.3. Задаваме проводниците с персонализирани имена - псевдоними (команда Place / Net Alias ...). Не забравяйте, че веригата с името трябва да бъде "облегната" на проводника, който назовавате, така че да докосва веригата.

Следователно, след като завършите чертежа, е необходимо да извършите автоматично опаковане на елементи в кутии. Извършвайки тази работа, не забравяйте да поставите отметка в квадратчето Безусловна референтна актуализация в диалоговия прозорец Анотиране в прозореца Действие - актуализиране на референтните обозначения и информацията за опаковане на всички елементи на веригата.

Разбира се, положителният резултат радва, но ние толкова бързахме да го получим, че пренебрегнахме някои много важни операции. Те не са задължителни за изпълнение, но за сложни проекти няма да са излишни.

Командата вече е достъпна за изпълнение. Щраквайки върху него с мишката, ще видим диалогов панел със съответното име (фиг. 11). Ниеискаме да контролираме не само грешките, но и предупрежденията, затова поставяме отметка в квадратчето Създаване на DRC маркери за предупреждения. Освен това, за да видите резултатите от проверката на екрана, поставете отметка в квадратчето Преглед на изхода. В този случай те ще бъдат записани във файла *.drc (в този пример във файла mux4.drc) и съдържанието му ще се покаже на екрана.

В него не са регистрирани грешки. Разбираемо е, защото резултатите от симулацията са очевидни. Но вижте колко много предупреждения. Така че не сме подобрили нищо. По принцип коментарите се свеждат до два вида:

- Мрежата няма източник на задвижване A1 - веригата няма източници на стартиране;

- Мрежата има по-малко от две връзки Q - мрежата има по-малко от две връзки.

Ако погледнете електрическата схема, ще видите DRC маркери (малки зелени пръстени) върху нея. Двойното щракване върху маркер отваря панел, обясняващ естеството на грешката или предупреждението. След като се справихме с естеството на предупрежденията, ще се опитаме да ги елиминираме. Оказва се, че цялата работа е, че не сме „закачили“ йерархични портове на входните и изходните вериги.

Активирайте командата Place/Hierarchical Port… или щракнете върху иконата. Нека поставим входните (PORTRIGHT-L) и изходните (PORTLEFT-L) портове на диаграмата, като ги наименуваме със същите имена като мрежите, към които са свързани. След като повторихме проверката на веригата, ще открием със задоволство, че сега има не само грешки, но и предупреждения (фиг. 12).

Позволете ми да ви напомня, че йерархичните портове също са необходими, за да генерирате автоматично обвивка на тестов стенд, в която по-късно можете да въведете VHDL тестови набори от входни сигнали. Технологията за създаване на такива VHDL тестове беше обсъдена в предишния урок.

- Steshenko V. B. ALTERA FPGA: дизайнустройства за обработка на сигнали. М. ДОДЕКА. 2000 г.

- Шалагинов А. В. Цифрово моделиране в CAD DesignLab 8. Уроци за начинаещи: Proc. надбавка. Новосибирско издателство на NSTU. 2000 г.