Описание на устройството

Основната памет на компютрите е реализирана на сравнително бавна динамична памет (DRAM), достъпът до нея води до прекъсване на процесора - появяват се цикли на изчакване (състояния на изчакване). Статичната памет (SRAM), изградена, подобно на процесор, върху тригерни клетки, по своята същност е в състояние да настигне съвременните процесори по отношение на скоростта и да направи циклите на изчакване ненужни (или поне да намали броя им). Разумен компромис за изграждане на икономични и продуктивни системи беше йерархичен начин за организиране на RAM. Идеята е да се комбинира голяма DRAM основна памет със сравнително малък кеш на бързи SRAM чипове.

Всеки път, когато има достъп до паметта, кеш контролерът проверява директорията, за да види дали има валидно копие на исканите данни в кеша. Ако е там, тогава това е случай на кеш хит (cache hit), а данните се вземат от кеша. Ако няма валидно копие, това е пропуск в кеша и данните се вземат от основната памет. Според алгоритъма за кеширане, блок от данни, прочетен от основната памет, при определени условия ще замени един от кеш блоковете. Процентът на попаденията и следователно ефективността на кеширането зависи от интелигентността на заместващия алгоритъм. Търсенето на блок в списъка трябва да се извършва достатъчно бързо, така че „обмислеността“ при вземането на решение да не отменя печалбата от използването на високоскоростна памет.

Достъпът до основната памет може да започне едновременно с търсене в директорията, а в случай на попадение може да бъде прекъснат (Look aside architecture). Това спестява време, но ненужният достъп до основната памет води до увеличаване на консумацията на енергия. Друг вариант: достъп до външна паметстартира само след коригиране на пропуск (Look Through архитектура), в този случай се губи поне един процесорен цикъл, но се пести енергия.

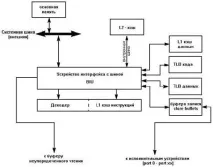

В съвременните компютри кеш паметта обикновено е изградена по схема на две нива. Основният кеш (L1 Cache) е вграден във всички процесори от клас 486 и по-стари; това е вътрешен кеш. Обемът на този кеш е малък (8-32 KB). За да се подобри производителността, често се използва отделен кеш за данни и инструкции (така наречената Харвардска архитектура е обратното на Принстънската, която използва споделена памет за инструкции и данни). Вторичният кеш (L2 Cache) за процесорите 486 и Pentium е външен (инсталиран на дънната платка), докато за P6 се намира в същия корпус с ядрото и е свързан към специална процесорна вътрешна шина.

Кеш контролерът трябва да осигури кохерентност - съгласуваността на данните от кеш паметта на двете нива с данните в основната памет, при условие че тези данни могат да бъдат достъпни не само от процесора, но и от други активни (busmaster) адаптери, свързани към шините (PCI, VLB, ISA и др.). Трябва също да се отбележи, че може да има няколко процесора и всеки може да има собствен вътрешен кеш.

Кеш линиите за показване на блок памет се разпределят при пропускане на операции за четене, в P6 редовете се запълват по време на запис. Блок, който няма копие в кеша, се записва в основната памет (за подобряване на производителността записът може да се извърши чрез буфер за обратно записване). Поведението на кеш контролера по време на операция за запис в паметта, когато копие на исканата област е в някакъв кеш ред, се определя от неговия алгоритъм или политика за запис (Write Policy). Има две основни политики за запис на данни от кеша в основната памет: WT за запис(Write Through) и WB (Write Back) обратно записване.

Политиката на WT е да изпълнява всяка операция за запис (дори еднобайтова), която въвежда кеширан блок както в реда на кеша, така и в основната памет едновременно. В този случай процесорът по време на всяка операция за запис ще трябва да извърши относително дълъг запис в основната памет. Алгоритъмът е доста лесен за изпълнение и лесно гарантира целостта на данните чрез постоянно съпоставяне на копията на данни в кеша и основната памет. Не е необходимо да съхранява признаци на присъствие и модификация - само информацията за етикета е напълно достатъчна (предполага се, че всеки ред винаги отразява някакъв блок, а кой - показва етикета). Но тази простота идва за сметка на ниската ефективност на записа. Има варианти на този алгоритъм, използващи забавени буферирани записи, при които данните се записват в основната памет през FIFO буфера по време на цикли на свободната шина.

Политиката на WB ви позволява да намалите броя на операциите за запис в основната шина на паметта. Ако блокът памет, в който трябва да се запише, е съпоставен с кеша, тогава първо ще бъде направен физически запис в тази валидна линия на кеша и той ще бъде маркиран като мръсен или модифициран, т.е. за изместване в основната памет. Само след това разтоварване (записване в основната памет) линията ще стане чиста (чиста) и може да се използва за кеширане на други блокове, без да се губи целостта на данните. Данните се записват в основната памет само като цял ред. Това разтоварване от контролера може да бъде отложено до спешен случай (достъп до кешираната памет от друг абонат, замяна на кеша с нови данни) или извършено в свободно време след модификацията на целия ред. Този алгоритъмпо-труден за изпълнение, но много по-ефективен от WT. Поддръжката на дънната платка за кеширане при обратно запис изисква обработка на допълнителни интерфейсни сигнали за изчистване на модифицирани линии в основната памет, ако тази област е достъпна от контролери на шини като други процесори, графични адаптери, дискови контролери, мрежови адаптери и т.н.

В зависимост от начина, по който линията на кеша и областта на основната памет са съпоставени, се разграничават три архитектури на кеша: кеш с директно картографиране, напълно асоциативен кеш и комбинация от тях - частично или зададено асоциативен кеш (set-associative cache).