Sharc Signal Processor Ръководство за потребителя - страница 13

Памет5

За съхранение на програми и данни, процесорите ADSP 2106x имат голямо количество двупортова памет в чипа. Паметта е разделена на два блока, наречени блок 0 и блок 1. Количеството налична памет в процесорите ADSP-2106x е показано по-долу:

брой 48 битови думи

брой 32 битови думи

брой 16 битови думи

32-битовите думи се използват за представяне на стандартни IEEE данни с плаваща запетая с единична точност. 48-битовите думи съдържат инструкции или 40-битови данни с плаваща запетая с висока точност. В допълнение, ADSP-2106x поддържа 16-битов формат на кратка дума за представяне на цели или дробни данни.

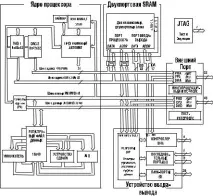

Във всеки процесор ADSP-2106x паметта е свързана с други функционални единици чрез три вътрешни шини: шина за програмна памет (PM), шина за памет за данни (DM) и шина за вход/изход (I/O). Шината PM и шината DM споделят един порт за памет, а I/O шината споделя друг. Вътрешните PM и DM шини се управляват от ядрото на процесора, I/O шината се управлява от входно/изходното (IOP) устройство, разположено на ADSP 2106x чипа. I/O шината позволява паралелен трансфер на данни между всяка памет и комуникационните портове на ADSP-2106x (портове за връзка, серийни портове и външен порт).

С такава двупортова структура за достъп до вътрешната памет на ядрото

процесор и входно/изходни устройства се извършват независимо според

отношение един към друг. В един цикъл всеки блок памет може

адресират както ядрото на процесора, така и I/O устройството, и когато ядрото

тогава процесорът и I/O адресират един и същ блок

не са необходими допълнителни цикли.

Външната памет може да бъде 16, 32 или 48 бита; контролерът за директен достъп до паметта (DMA) автоматично пакетира външни данни в думи с подходяща битова ширина: 48-битови инструкции или 32-битови данни. Имайте предвид, че вътрешната памет е разделена на два блока, наречени блок 0 и блок 1, докато външната памет е разделена на четири банки.

5.1.1. Двоен достъп до данни

В процесорите от семейството ADSP 2100 и ADSP 21000 паметта традиционно се разделя на програмна памет (за съхраняване на инструкции) и памет за данни (за съхраняване на данни). Модифицираната процесорна архитектура на Harvard се характеризира с възможността за съхраняване на данни в програмната памет. ADSP 2106x поддържа разделянето на шините в чипа на отделни шини за програмна памет и памет за данни (както във фамилията ADSP 21000), но не се ограничава до използването на един от двата блока памет за съхранение на програми и другия за съхранение на данни. Тази организация ви позволява свободно да конфигурирате паметта за съхраняване на различни комбинации от код и данни.

Наличието на независими шини за програмна памет и памет за данни позволява на ядрото на процесора ADSP 2106x едновременно да осъществява достъп до команди и данни в двата блока памет. Ако трябва да осъществите достъп до две думи в един и същ блок от паметта (на една и съща шина), като използвате една инструкция, тогава ще е необходим допълнителен цикъл. Инструкциите се извличат от паметта чрез шината на програмната памет или от кеша на инструкциите. Данните могат да бъдат достъпни по шината на паметта за данни (с помощта на DAG1) и по шината на паметта на програмата (с помощта на DAG2). Схемата за свързване на шина ADSP 2106x е показана на фиг. 5.1.

Двата блока памет на процесорите ADSP 2106x могат да бъдат конфигурирани да съхраняват различни комбинации от 48битови инструкции и 32 битови данни. Въпреки това, максимална ефективност (т.е. изпълнение на две инструкции за достъп до данни в един цикъл) се постига, когато единият блок съдържа инструкции и данни от програмната памет, а другият блок съдържа само данни от паметта за данни. Това означава, че за инструкция, изискваща два достъпа до данни, PM шината (и DAG2) ще се използва за достъп до данни от блок, съдържащ както команди, така и данни, а DM шината (и DAG1) ще се използва за достъп до данни от блок само за данни и командата, която се извлича, трябва да е достъпна от кеша. Друг начин е да съхраните един операнд във външна памет, а другият във всеки блок от вътрешна памет.

При прилагане на цифрови филтри и бързо преобразуване на Фурие (FFT) с помощта на процесори, при изпълнение на някои инструкции трябва да има

налични са два операнда с данни. В цифров филтър, например, филтърните коефициенти могат да се съхраняват като 32-битови думи в същия блок от паметта, който съдържа 48-битовите инструкции, докато 32-битовите проби от данни се съхраняват в друг блок. Това позволява двойна инструкция за достъп до данни да бъде изпълнена в един цикъл, когато коефициентите на филтъра се извличат по PM шината с помощта на DAG2 и инструкцията е от кеша.

За да се осигури паралелен достъп до две области на паметта в един цикъл, трябва да бъдат изпълнени следните условия:

♦ командата трябва да е от следния тип:

(Имайте предвид, че четенето и писането са взаимозаменяеми).

Обърнете внимание, че ако избраната команда не е в кеша по време на предаване чрез DAG2, тогава ще възникне пропуск в кеша.

5.1.2. Кеш на инструкциите и достъп до данни по шината на програмната памет

Обикновено ADSP 2106x избира команди в 48битова шина на програмната памет (PMD). Въпреки това, когато процесорът изпълни инструкция за двоен достъп до данни, която изисква данните да бъдат прочетени от или записани в PMD шината, възниква конфликт при използване на тази шина. Кешът на командите разрешава този конфликт, като предоставя командата (стига да е кеширана след първото й изпълнение).

Предоставяйки инструкция, кешът позволява на ядрото на процесора да има достъп до данни в PMD шината; Ядрото на процесора извлича инструкцията от кеша, вместо да я извлича от паметта, така че данните да могат да бъдат прехвърлени към процесора по PMD шината едновременно с извличането на инструкцията. Само тези команди се поставят в кеша, когато са избрани от паметта, има конфликт с достъпа до данни през PMD шината.

Кешът на инструкциите позволява достъп до данните през PM шината без допълнителни цикли, ако инструкцията, която трябва да бъде извлечена, вече е кеширана. Дори ако командата и данните са в различни блокове памет,

но същата шина се използва за извличането им, винаги ще се добавя допълнителен цикъл в случай на неуспешен достъп до кеша.

ADSP 2106x има три вътрешни шини, свързани към неговата двупортова памет: PM, DM и I/O шини. Шините PM и DM споделят един порт за памет, а I/O шината споделя друг порт.

48-битовата PMD шина се използва за прехвърляне на команди (и данни), 40-битовата DMD шина се използва за прехвърляне на данни. Ширината на PMD шината е 48 бита в съответствие с дължината на командната дума. Когато тази шина се използва за прехвърляне на 32-битови данни с плаваща запетая или 32-битови данни с фиксирана запетая, данните се подравняват към 32-те най-значими бита на шината.

PX регистрите, свързващи шините, позволяват обмен на данни между 48между 40-битова PMD шина и 40-битова DMD шина или между 40-битов регистърен файл и PMD шина. Тези регистри съдържат хардуера за разрешаване на разликите в ширината на шината.

5.1.4. Комуникация между автобусите

PX регистърът осигурява обмен на данни между вътрешните шини: между 48-битовата PMD шина и 40-битовата DMD шина за данни. 48-битовият PX регистър се състои от два регистъра: 16-битов PX1 и 32-битов PX2. PX1 и PX2 могат да се използват независимо в инструкции и могат също да се разглеждат като комбиниран PX регистър. Поставянето на PX1 и PX2 в регистъра PX е показано на фигура 1 по-долу. 5.2.