Внедряване на PCI Express v3

Alpha-Data поема по различен път. Модулът ADM-PCIE-KU3-X16 няма превключвател. Но две x8 шини се извеждат към x16 конектора. FPGA може да реализира два независими контролера. За да направи това, FPGA има два сигнала за нулиране и две референтни честоти. Но този модул ще работи само в специални дънни платки, където два x8 също се извеждат към конектора x16. Не съм виждал такива дъна, но явно са.

Нашата компания реши да внедри модула FMC122P с вътрешен превключвател. Основната задача беше да се провери максималния обменен курс. Друга също толкова важна задача е да се постигне съвместимост със съществуващия софтуер и FPGA компоненти.

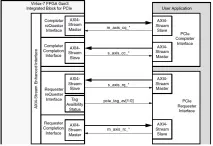

PCI Express контролерът за Virtex 7 е коренно различен от контролерите за Virtex 6, Kintex 7. Стана по-удобен, но е различен. Фигурата показва блоковата схема на контролера:

Контролерът има две части, Completer и Requester, всяка с две AXI_Stream шини. Заявките от шината PCI Express идват през възела Completer. Тези заявки се изпращат до шината m_axis_cq. Шината s_axis_cc трябва да получи отговор от потребителския компонент. Обикновено това е възел за достъп до вътрешните регистри на FPGA.

Чрез Requester възела на s_axis_rq шината, DMA контролерът изпраща заявки към PCI Express шината. Отговорите идват през шината m_axis_rc.

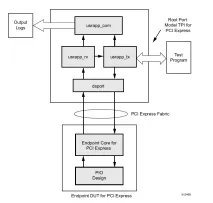

IP Core включва примерен проект, за да разберете как работи. Проектът е написан на Verilog и за съжаление може да служи и като пример как да не се развива. Нека да разгледаме блоковата диаграма на един пример.

Тази диаграма е взета от описанието на IP Core. На пръв поглед всичко е наред - това е прекрасна картина, може да се показва на мениджъри, ръководители на проекти, клиенти. Проблемите започват от реализацията. Има много места в тази система, където Verilog се използва за достъп до обекти по абсолютен път. Според мен в тази система това е оправдано само на едно място - това е заобикалянето на GTP възлите за моделиране на ниво PIPE. Но абсолютно не е необходимо да се прави връзка между userapp_tx и userapp_rx с помощта на абсолютни пътища.

В проект изглежда така:

Компонентът pci_exp_usrapp_tx има функцияTSK_SYSTEM_INITIALIZATION, която извиква функцията от pci_exp_userapp_cfg чрез абсолютен път:

board.RP.cfg_usrapp.TSK_WRITE_CFG_DW(по-нататък наричам функция това, което е описано във Verilog чрез задача). Разглеждаме компонента pci_exp_userapp_cfg, какво виждаме: cfg_ds_bus_number root_port

Чрез компонента rp0 се правят достъпи за писане или четене на 32-битови думи. Компонентът rp1 извършва само инициализация.

За съжаление, това се моделира много дълго време, дори ако симулацията се извършва на ниво PIPE. Типичната симулационна сесия е около десет минути (може би повече, не помня). Това не е подходящо за оперативна работа с DMA канал. В тази ситуация беше взето напълно естествено решение за премахване на PCI Express контролера от модела. Освен това вече е проучен.

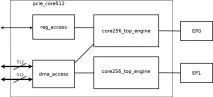

Блокова схема на контролера

Обобщена схема на контролера е показана на фигурата.

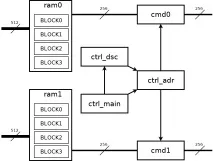

Два идентични компонента core256_top_engine осигуряват достъп до два контролера EP0, EP1. core256_top_engine осигурява достъп до регистрите от страната на PCI Express, за това се използва само EP0и компонента reg_access. Компонентът dma_access съдържа основната логика за управление на контролера. Неговата блокова схема е на фигурата по-долу:

Възелът dma_access е най-сложната част от контролера. Съответно трябва да се моделира особено внимателно. Както писах по-горе, симулацията на две PCI Express ядра отнема много време. За да се ускори, е разработен модел, който е свързан вместо core256_top_engine. За dma_access остава същият интерфейс и скоростта на симулация се е увеличила с порядък. В този проект, както и в проекта PROTEQ, се използва автоматично стартиране на тестове чрез tcl файл.

Ето фрагмент от tcl файла:

Това е автоматично изпълнение на девет теста. Например ще дам кода на един тест:

Логическа организация на контролера

На ниво регистър контролерът напълно повтаря предишните ни контролери за FPGA Virtex 4, Virtex 5, Virtex 6, Kintex 7; Организацията може да бъде намерена в проекта PCIe_DS_DMA. Характеристика на всички контролери е комбинацията от единични дескриптори в блок от дескриптори. Това дава драматично увеличение на скоростта при използване на фрагментирана памет.

Връзка с преносими компютри

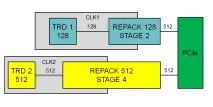

За нас е важно да свържем този контролер към нашите преносими компютри. Какво представляват тетрадите, написах в предишна статия: "ADM интерфейс: Какво е тетрада." Работата с 512-битова шина изисква промяна в подхода. За да свържа тетрада, трябваше да използвам допълнителен възел за преопаковане. Структурна схема - на фигурата.

Преопаковчикът изпълнява две задачи:

- проследяване на автобуса по протежение на чипа, за това можете да зададете броя на допълнителните етапи на тръбопровода

- връзка с преносими компютри с 64 и 128 битови шини

Крайната цел на разработването на контролер и свързването с тетради е да се получи непрекъснат поток от данни от ADC към компютъра. И тук се сблъскваме с факта, че шината PCI Express не осигурява стабилна скорост. Възможни са закъснения на автобуси. Това е особено забележимо при високи валутни курсове. Закъсненията възникват поради работата на други устройства. Стойността на закъснението може да бъде различна, може да бъде 5 - 10 µs, или може би повече. Закъснение от 10 µs при 11 GB/s съответства на блок памет от 110 килобайта. За вътрешна памет дори съвременните FPGA са много. Но забавянето може да е още по-дълго. Ако потокът от данни не може да бъде поставен на пауза, какъвто е точно случаят, когато се използват ADC, тогава буферирането във външна памет е единственият изход. Освен това паметта трябва да може да работи със скорост от 22 GB / s. Имаме два SODIMM DDR3-1600 инсталирани на модула. Паметта работи на 800 MHz. Това съответства на непрекъснат поток от данни от 8400 MB/s. Тази цифра се потвърждава от експеримента. Искам да отбележа, че скоростта от 8400 MB / s надвишава скоростта на извеждане на данни от най-бързия ни подмодул, който има два ADC на 1800 MHz.

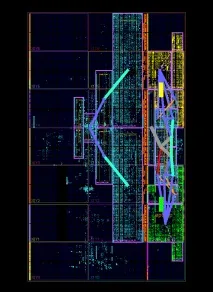

Екранната снимка показва резултата от трасирането в програмата PlanAhead:

Картината показва два PCI Express контролера (маркирани в жълто и зелено) и два контролера на паметта (до PCI Express).

Както се оказа, подобен проект е много труден за Вивадо, тя се справя много зле с него. Един проект във Vivado е лошо възпитан и често просто не работи. ISE показва много по-стабилни резултати. PCI Express възлите са свързани в съответствие с препоръките на Xilinx, но се оказа, че те са раздалечени на чип. А това вече създава проблем за споделянедруги мулти-гигабитови линии.

На компютър с DDR3-1600 памет, когато проверката е активирана, скоростта пада до 8500 MB/s.

На компютър с DDR3-1866 скоростта не намалява с един модул и включена проверка.

Два модула FMC122P в компютър с DDR3-1866 без тестване също показват максимална скорост от около 11000 MB / s за всеки модул. Но когато включите проверката, скоростта пада.

С тези измервания се приема, че 1 MB е 1024 KB, а 1 KB е 1024 байта.

Бих искал да отбележа, че в тази работа представям резултата от работата на голям екип. Специални благодарности на Дмитрий Авдеев, който свърши чудесна работа по този проект.