Заличаване на крайните нули

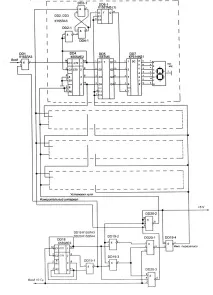

Сглобен е броячен блок от шест декади, който може да се използва в честотомери, мултиметри и др. със схема за заглушаване на незначещите нули. Много е удобно да се въведе тази схема за потискане на незначителни нули в десетилетия, където има декодери със специален изход за контрол на индикацията (гасене). Например K, KR514D1, ID2, K176ID2, IDZ и др. Ако изходните етапи са направени на други декодери, това също няма значение. Можете да промените всяко десетилетие. Основното тук е да разберете принципа - ако след нулевия импулс за настройка броячът на всяко десетилетие работи поне веднъж, тогава ще е необходимо индикаторът да светне, ако броячът не работи, тогава няма нужда да го светвате. Следователно, ако във веригата се използват други декодери, тогава просто ще е необходимо да добавите ключ в захранващата верига към всеки индикатор (един транзистор), който ще се управлява от сигнал от RS резето. Допълнителните елементи, които трябва да бъдат въведени, са показани с брояч от четири десетилетия като пример. Схемата е много проста и е направена на достъпна и евтина материална база.

Нека анализираме принципа на действие на схемата за заличаване на незначителни нули от първото десетилетие. Блокът за управление при подаване на импулси с честота 10 Hz на входа му генерира импулс на интервал на измерване с продължителност една секунда, както и импулси за пренаписване на тригери на паметта и импулси за нулиране на декадни броячи и RS клетки (резета). За генериране на измервателен интервал с продължителност 0,1 секунди е необходимо да се подадат импулси от кристален осцилатор с честота 100 Hz към входа на контролния блок и т.н., тъй като контролният блок разделя входящите импулси на 10. След преминаване на импулсите за настройка на нулата, всички тригери, както и RS-ключалки, които се правят на елементите OR-NOT, микрочирата DD1 LE1 cuts са зададени на нула. На щифт 1чип D1 има ниво на логическа нула. От изход 14 на гасителния тригер DD6.1 се подава ниво на логическа нула към изход 3 на декодера, което забранява индикацията. Сглобих веригата дълго време и сега не си спомням защо поставих тригерите след ключалките. Възможно е те да са излишни и да могат да бъдат премахнати, тъй като повтарят сигнала на резето. Диаграмата ще бъде малко опростена. След прилагане на импулси за броене към входа, първият импулс води до появата на логическа единица на пин 12 на чипа DD4. RS-фиксаторът на елементите DD2.1, DD2-2 се задейства (заключва) и впоследствие не реагира на импулси, идващи от брояча. На пин 1 елемент DD2.1 се появява нивото на логическа единица. В зависимост от броя битове, получени на входа на брояча, логически единици се появяват в същия брой битове на изходите на RS-ключалките - позволяващи индикацията към декодерите. След края на измервателния интервал управляващият блок генерира импулси за пренаписване на тригерите на паметта, както и импулси за настройка на нула, след което цикълът се повтаря. RS-резета могат да бъдат направени и върху 2I-NOT елементи. Тъй като логиката на работа на RS-тригери, сглобени на тези елементи, се различава от работата на тригери, сглобени на елементи OR-NOT (RS-ключалките се управляват от входове с импулси с ниво на логическа нула), веригата претърпява незначителни промени.

Входът на демпферния тригер DD6.1 е свързан към долния изход на RS ключалката. Входящите импулси от брояча трябва да се инвертират (добавя се още един LAZ инвертор). Импулсите за нулева настройка на RS-ключалките трябва да се подават от клеми 6.9 на микросхемата DD20 на управляващия блок (т.е. той също трябва да бъде обърнат). Задействанията на паметта DD5 могат да бъдат пропуснати, ако желаете. Те са предназначени да предотвратят мигането на индикаторите по време на броене на импулса.Но с тях работата на индикаторите е много по-приятна. Микросхемите могат да бъдат приложени към всяка (TTL) серия, 555, 1533, 1555, 133, 531 и т.н. Вместо TM5 можете да използвате TM7, още по-добре е да използвате регистър, например K533IR22, тъй като съдържа 8 тригера, тогава за 8-битов честотен брояч (за заличаване на 8 бита и за десетилетна памет) ще ви трябват само 5 регистъра (10 случая TM5). Регистърът е активиран, както следва. Входове - 3. 4. 7. 8. 13. 14. 17. 18;, изходи, съответно - 2. 5. 6. 9. 12. 15. 16. 19. Щифтове 1 и 10 са свързани към общ проводник, а на щифт 11 се подават импулси за презапис. Можете също така да приложите регистрите IRZZ, IR34 от всяка TTL серия.

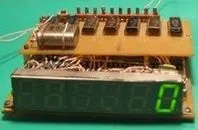

На снимките можете да видите работата на гасителната верига за незначителни нули при различни честоти на входа. Да, при сглобяването на веригата реших да оставя (не да изгася) първата нула от десетилетието на преизчисляване, като индикатор за включване на устройството (първата снимка).

Използвана литература: ВРЛ, 1983г. 84 брой, стр. 13-22. Б. L. Shilo - "Популярни цифрови схеми".