Абстрактна система в реално време

21 Система в реално време е тази, при която успехът на изчисленията зависи не само от тяхната логическа коректност, но и от времето, когато резултатите от изчисленията са готови. Ако времевите ограничения не могат да бъдат изпълнени, тогава е възникнала системна грешка.

Системите на преден план/заден план са еволюция на системи само за прекъсване, в които цикълът на запитване е заменен от код, който извършва полезна обработка на данни. Използването на системи на преден план/фон е често срещан подход за вградени приложения. Те включват набор отзадвижвани от прекъсванеилипроцеси в реално време, нареченипреден план, и набор отзадвижвани от прекъсванепроцеси, нареченизаден план.

Решаването в реално време на всички проблеми са отделни случаи на приоритетни/фонови системи. Например, кръговият режим е проста фонова система без задача на преден план и цикли на анкета като задача на фона. Добавянето на прекъсвания за синхронизиране ще даде фонова система с пълен приоритет. Кодът, управляван от прекъсване, е фонова система на преден план без задачи на преден план и код, управляван от фазов процес, като фонова задача. Съвременните системи са просто сложен фонов процес. И накрая, системите само за прекъсване са системи на преден план/заден план без фонова обработка.

Точно като непрекъсваема сервизна задача, фоновата обработка не трябва да включва критични за времето задачи. Тъй като фоновият процес е процесът с най-нисък приоритет, почти 100% от времето. Винаги трябва да се изпълнява в крайната фаза на обработка, а нене трябва да има блокиращи ситуации по време на изпълнение. Например, в повечето случаи, когато се изпълнява задача във фонов режим, съдържанието на брояча на команди се увеличава, за да се превключи към измерване на времето за зареждане или да се определи дали задачата на преден план виси. Също така е желателно да се осигурят отделни броячи за процеси на преден план, които нулират фона. Ако фонов процес открие, че един от броячите не се нулира достатъчно често, тогава е възможно съответната задача да не се изпълнява, което може да означава, че е открито състояние на грешка. Този подход се наричапрограмируем пазач. Някои видове самотестове с нисък приоритет също могат да се извършват във фонов режим. Например, много системи изискват извършването на пълен тест на командите на процесора. Този тип тестване никога не се извършва на преден план, но трябва да бъде част от подобряването на надеждността. Проектирането и кодирането на тези CPU тестове изисква внимателно планиране. Актуализациите на дисплея с нисък приоритет, записите на принтера и други бавни операции на устройството трябва да се извършват във фонов режим.

22.Режим в реално време– режим на обработка на данни, който осигурява взаимодействието на изчислителната система с външни за нея процеси със скорост, съизмерима със скоростта на тези процеси.

23.

24. Както вече беше споменато, RTS е софтуерен и хардуерен комплекс, който наблюдава обект и/или го управлява при времеви ограничения. Събитията, настъпващи на обекта, подлежат на обработка в RTS. Ще възложим задача на всеки тип събитие.

ЗАДАЧА (ЗАДАЧА)- блок от програмен код, отговорен за обработката на определени събития,възникващи в контролния обект.

Задачата може да бъде "рамкирана" във формата:

- отделен процес

- Поток на контрол в рамките на процес (нишка, лек процес)

- Обработчик на прекъсване/подпрограма

РАБОТА НА РАБОТА (РАБОТА)- процесът на изпълнение на блок програмен код по време на обработка на събитие.

Всяка работа от задачата се характеризира със следните времеви параметри:

- r (Време за освобождаване)- моментът, в който задачата стане готова за изпълнение (например процесът влиза в състояние на готовност)

- d (Абсолютен краен срок)- абсолютен краен срок, моментът от време, до който задачата трябва да завърши следващата работа.

- s (Начално време)- моментът, в който задачата е започнала да се изпълнява на процесора

- s (Време за изпълнение)- моментът, в който задачата е завършила работата си чрез обработка на събитието

- D (Относителен краен срок)- относителен краен срок. D = d - r

- e (Време за изпълнение)- време за изпълнение на задачата, когато изпълнява следващата си работа. e = c - s

- R (Време за реакция)- време за реакция. R = c - r

Диаграмата по-долу илюстрира тези опции:

0 1 2 3 4 5 6 7 8 9 10 11 12 13

Операцията на задачата, показана на тази диаграма, има следните параметри:

- r=2

- d=11

- s = 5

- c = 9

- D=11 - 2=9

- e = 9 - 5 = 4

- R=9 -2=7

Споменатите параметри се определят, както следва:

- Времената, когато задачите преминават към състояние на готовност, всъщност се определят от естеството на управлявания обект.

- Сроковете се определят от разработчика на RTS въз основа на свойстватауправляван обект.

- Времената за изпълнение на задачите се определят от архитектурата на процесора, неговата тактова честота и конкретната реализация на конкретен алгоритъм.

- За определяне на последната стойност могат да се използват 2 подхода.

- Първият е да се преброи броя на процесорните цикли, необходими за изпълнение на определена задача. Имайте предвид, че такова изчисление става изключително сложно, ако процесорът съдържа механизми като конвейери и различни кешове.

- Вторият подход е по-прост и се състои в това, че времето за изпълнение се измерва директно. Отбележете отново, че в случай на процесори с конвейери и кеш памети, такива измервания не гарантират, че ще бъде измерено точно МАКСИМАЛНОТО време за изпълнение на определен код (. ). И накрая, системите, използващи механизми за пейджинг, също са по-малко предвидими и следователно се считат за "врагове" на системите в реално време. Не е за нищо, че различни видове стандарти, свързани с RTS, предоставят средства за блокиране на страници с памет.

25. ПРОГРАМИРУЕМ I/O

Програмираният I/O използва специален процесор за прехвърляне на данни. Инструкцията за вход (вход) прехвърля данни от определеното I/O устройство към посочения регистър на процесора. Командата за изход (out), прехвърля данни от регистъра на процесора към определеното I / O устройство. Обикновено идентифицирането на оперативния регистър на процесора е вградено в подкоманди. Както командата за въвеждане, така и командата за изход изискват ресурси на процесора и на първо място време, което се отразява на производителността в реално време.

Следният кодов фрагмент задава скоростта на въртене на двигателя (вижте Фигура 7.1).

Първите две инструкции на кода инициализират съдържанието на REGISTER 1и 2. След това се изпълнява командата Out.

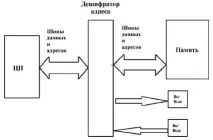

26. Директен достъп до паметта (DMA/DMA)

Паметта се предоставя на други устройства в системата без намесата на процесора, тоест информацията се въвежда директно в RAM на външно устройство. Ако веригата DMA не е интегрирана в чипа на процесора, тогава е необходим DMA контролер, тъй като такава схема не изисква участието на процесора в преноса на данни, самият трансфер на данни е бърз.

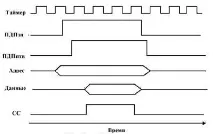

DMA контролерът предотвратява ситуации, като изисква всяко устройство да има "DMA сигнал за заявка", който трябва да бъде потвърден от "DMA сигнал за потвърждение" от контролера. Докато не бъде изпратен сигнал за потвърждение към заявителя, неговата връзка с главната шина е в състояние на три състояния. Всяко устройство, което е в състояние на три състояния, не може да повлияе на данните на шината на паметта. Веднага след като "сигналът за потвърждение на DMA" бъде изпратен до искащото устройство, проводниците на неговата шина на паметта стават активни и данните се прехвърлят, точно както данните се обменят с процесора.

27.

I/O, използвайки специална памет

Като пример, разгледайте контрола на скоростта на стъпков двигател. Ако е необходимо да се приложи I / O с помощта на разпределена памет, асемблиращият код ще бъде както следва:

28. Побитово изобразяване на устройства