D-тригер с работа на ниво (резе) и отпред - Помощ за инженер, Диаграми, принцип на работа,

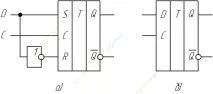

D-тригерът получи името си от английската дума "закъснение" - забавяне, което се реализира чрез прилагане на сигнали към входа за синхронизация. Обсъденият по-рано тригер RS имаше два входни сигнала, но за предаване на двоичен код е достатъчен един вход с различни нива на напрежение: високо (1) и ниско (0). Човек не може да бъде приложен към два входа едновременно, следователно в D тригера тези входове се комбинират с помощта на инвертор (Фигура 1 а), което елиминира възможността за забранено състояние.

Фигура 1 - a) подобрена схема на RS-тригера b) графично представяне на D-тригера

Trigger D може да работи според нивото на сигнала, нарича се още резе. В такова устройство е необходимо да се ограничи продължителността на синхронизиращия сигнал, тъй като докато се прилага синхронният сигнал, преходният процес от входа преминава към изхода.

Схема на ключалката, монтирана върху логически елементи 2OR-NOT (син проводник - логическа нула, червен - едно):

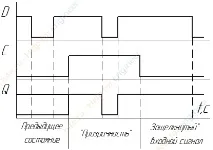

Времева диаграма на работа:

Тригерът за блокиране се активира само от синхронизиращ сигнал. Когато C е логическа нула, тогава изходът Q съхранява миналото състояние, записано на него, докато нивото на напрежение на вход D не може да го повлияе по никакъв начин. Ако приложите "1" към входа за синхронизация, устройството ще работи в режим "прозрачност" - изходният сигнал незабавно повтаря входния сигнал. Но когато часовниковият сигнал е изключен, последното състояние на входа ще остане в паметта на тригера и ще бъде на Q. Това означава, че се оказва „затворен входен сигнал“.

Въз основа на описания принцип на работа ще съставим таблица на истината:

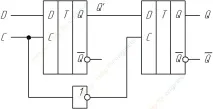

D тригер, работещ по фронта, не трябва да контролира продължителността на синхронизиращия (тактов) сигнал, тъй като фронтът на сигнала C преминавапочти моментално (не може да продължи дълго време). Тригер, който ще съхранява информация само на ръба на часовниковия сигнал, може да бъде изграден от два D-тригера, часовниковият сигнал към които ще се подава в противофаза:

Съответно, верига на логически елементи може да бъде конструирана с помощта на четири ИЛИ-НЕ и един обратен блок:

На фигура 2 (анимация), в горния десен ъгъл, за по-лесно възприемане, числото "1" е изписано на първия кадър. Като започнете да разглеждате от тази рамка, ще бъде по-лесно да проследите принципа на работа (син цвят - "0", червен - "1").

Времева диаграма на D-тригер, работещ отпред

Помислете за принципа на работа. Q' е изходът на първия тригер, Q е изходът на втория. Тъй като часовниковият сигнал към първия и втория вход е обърнат, когато единият е в режим на съхранение, другият пропуска информация от входа към изхода. Диаграмата показва, че стойността на изхода на тригера Q ще се промени само при падащия фронт на синхронизиращия (тактов) сигнал C. Тоест стойността при Q ще съответства на напрежението на входа D в момента, в който часовниковият сигнал се промени от 1 на 0.

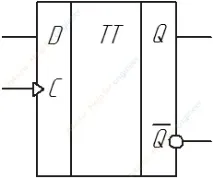

Тъй като това устройство се състои от две по-прости устройства, конвенционалното му обозначение е както следва:

Където TT означава наличието на два прости тригера в структурата, а „триъгълникът“ близо до вход C означава, че тригерът работи на фронта на сигнала.