Двоични декодери

Декодерите са преобразуватели на кодове. Двоичните декодери преобразуват двоичния код в код "1 от N". В кодовата комбинация на този код само една позиция е заета от единица, а всички останали са нула. Например код "1 от N", съдържащ 4 кодови комбинации, ще бъде представен по следния начин:

От казаното се вижда, че двоичен декодер с n входа трябва да има 2 n изхода, съответстващи на броя на различните; комбинации в n-битов двоичен код.

В зависимост от входния двоичен код, една и само една от изходните вериги се възбужда на изхода на декодера.

Ако част от входните набори не се използва, тогава декодерът се нарича непълен и неговият брой изходи е по-малък от 2 n .

Ориз. 2.4. Символ (а) и схемно изпълнение (б) на двоичен декодер

Буквите DC (от англ. Decoder) се поставят в символа на декодера: Обичайно е входовете на декодера да се обозначават с техните двоични тегла. В допълнение към информационните входове, декодерът обикновено има един или повече входове, разрешенията за работа са обозначени като EN (Enable). Ако този вход е активиран, декодерът работи, както е описано по-горе; ако не е активиран, всички изходи на декодера са пасивни. Ако има няколко входа за разрешаване, тогава сигналът за разрешаване на операцията се формира като комбинация от сигналите на отделните входове. Условното графично обозначение на пълния двоичен декодер е показано на фиг. 2.4,а.Често декодера има инвертирани изходи. В този случай само един изход има стойност нула, а всички останали имат стойност единица. Когато декодерът е деактивиран, всички негови изходи ще имат логическа единица.

Функционирането на декодера се описва от системата от връзки:

Схемно изпълнение на декодери

Схематично, декодерът е набор от конюнктори (или NAND елементи в декодери с обърнати изходи), които не са свързани помежду си. Всеки конектор (или NAND елемент) генерира една от изходните функции. В допълнение към елементите за генериране на изходни функции, декодерът, подобно на много други ИС, е оборудван със схеми за генериране на двуфазни сигнали от еднофазни (директни) входове към входовете на ИС. Имайте предвид, че входната права линия не се използва директно във веригата, а се генерира многократно като двойна инверсия от входа. Това се прави, за да се разтоварят максимално външните входни линии (тук външните входове се зареждат само на един вход на инвертора) * Външните входни линии винаги са разтоварени до максимум, тъй като те вече са натоварени с капацитет поради тяхната относително голяма дължина и конструкцията на щифтовете на IC пакета, което намалява скоростта на предаване на сигнала по линията.

Съкратена схема на декодера, показваща един входен ред и един изходен ред (за по-голяма яснота е взет редът с номер 5) е дадена на фиг. 2.4,б.

Време за установяване на изхода на декодера

където tz.inv. - забавяне на сигнала в инвертора; t, 10,1z 01 - закъснения на превключване на логическия елемент.

Вижда се, че декодерът е един от високоскоростните възли.

Както е известно, IC пакетите с голям брой изводи са трудни за производство и са скъпи. От тази гледна точка декодерите са изключително неуспешни схеми, тъй като имат много външни изводи с проста вътрешна структура и малък брой елементи на веригата. Само декодер с 4 информационни входа е подходящ за поставяне в обикновен евтин калъф. В серията IS вече няма "размерни" декодери.

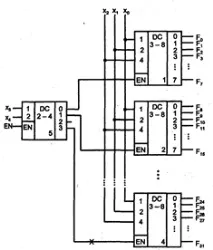

Ориз. 2.5. Схема за двоично мащабиранедекодер

Увеличаване на размера на декодера

Малкият капацитет на стандартните декодери поставя въпроса за увеличаване на капацитета им. От нискобитови декодери можете да изградите схема, еквивалентна на декодер с по-голям битов капацитет. За да направите това, въведената дума е разделена на полета. Битовата дълбочина на полето на най-малките битове съответства на броя на входовете на наличните декодери. Оставащото поле от най-значимите цифри се използва за получаване на сигнали, които да позволят работата на един от декодерите, които декодират полето от най-малко значимите цифри.

Като пример, на фиг. 2.5 показва схема за декодиране на петбитов двоичен код с помощта на декодери "3-8" и "2-4" - За получаване на необходимите 32 изхода се съставя колона от четири декодера "3-8". Декодерът "2-4" взема двата най-значими бита от входния код. Възбуден единичен изход на този декодер отключва един от колонните декодери на неговия вход за разрешаване. Избраният декодер на колони декодира най-малко значимите три бита от входната дума.

Всяка входна дума отговаря на възбуждането само на един изход. Например, при декодиране на думата X4X3X2X1X0 = 110012 = 2510, входът на декодера от първия слой има код 11, който възбужда неговия изход номер три (показан с кръст), което позволява на DC4 да работи. Код 001 действа на входа на DC4, така че единицата ще се появи на първия си изход, т.е. на 25-ия изход на веригата като цяло, което е необходимо.

Общото разрешение или забрана на работата на веригата се извършва на входа EN на декодера на първия слой.

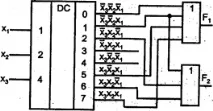

Ориз. 2.6. Схема за възпроизвеждане на произволни логически функции с помощта на декодер. и дизюнктори

Декодерите, заедно с ИЛИ схемите, могат да се използват за възпроизвеждане на произволни логически функции. Наистина, на изходите на декодера, всичкисъединителни термини (компоненти на единица), които могат да бъдат съставени само от даден брой аргументи. Логическа функция в SNDF е дизюнкция на известен брой такива термини. Събирайки необходимите термини според схемата ИЛИ, можете да получите всяка функция от даден брой елементи.

На фиг. 2.6 като пример е показана диаграма на развитието на две функции

. Такова решение може да е подходящо, когато е необходимо да се разработят няколко функции на едни и същи аргументи. В този случай се добавя само един дизюнктор за генериране на допълнителна функция. Имайте предвид, че за да проверите правилността на веригата на фиг. 2.6 е удобно да се преведат функциите и в SDNF.