Локална PCI шина - Авдеев В

5.2. Локална PCI шина

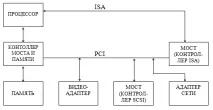

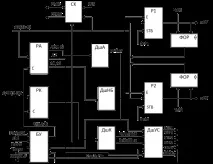

PCI шината е проектирана да работи с 5V или 3.3V захранващо напрежение и може да се използва в сървъри, настолни компютри, лаптопи и лаптопи. Платките с различни захранвания имат специални ключове на някои места на контакти, освен това характеристика на PCI шината е, че тя не е свързана с конкретен тип компютър и е проектирана да се използва в нови системи. На фиг. 5.1 показва възможна конфигурация на компоненти, свързани към PCI шината.

Ориз. 5.1. Схема на свързване на компоненти към PCI шината

Помислете за предназначението на основните сигнали на PCI шината. Символът # след името на сигнала на PCI шината показва, че активното ниво на този сигнал е ниско (логическа 0). В допълнение, обозначението, например (31-0), дефинира група линии (сигнали) с номера от 31 до 0, t / s е двупосочен I / O сигнал с три състояния, s / t / s е активен активен сигнал с ниско ниво с три състояния, in е стандартен входен сигнал, out е стандартен активен драйвер, o / d е отворен дренаж за комбиниране на сигнали (OR).

PAR t/s – равен паритет на AD(31-0) и C/BE(3-0)# сигнали за всички агенти на PCI шина.

FRAME# t/s – цикъл на кадрите. Този сигнал се задава от инициатора и показва началото на автобусна транзакция, премахването на сигнала означава крайната (крайна) фаза на данните.

IRDY# s/t/s – готовност на инициатора. Мастерът генерира този сигнал, ако може да изпраща или получава данни. Сигналът IRDY# се използва заедно със сигнала TRDY#. Фазата на данните се изпълнява, когато сигналите IRDY# и TRDY# са активни (ниски). Ако поне един от тези сигнали е пасивен (висок), циклите на изчакване се вмъкват в операцията на инициатора.

TRDY# s/t/s - Готовността на целта показва способността на избраното устройство да завърши текущата фаза на данни. При четене TRDY# показва валидността на предадените данни, а при запис готовността на целта да получи данни.

STOP# s/t/s – стоп. Целевият сигнал казва на капитана да постави на пауза текущото събитие.

IDSEL# in – избор на устройство за инициализация. Сигналът се генерира от главния или PCI-PCI моста за избор на устройство при запис или четене на конфигурационната му памет.

Следващата група сигнали е свързана с арбитраж и се използва само от инициаторите за улавяне на шината.

REQ# t/s – заявка. Показва на арбитъра, че инициаторът изисква PCI шина. Всеки инициатор задава свой собствен REQ#.

GNT# t/s – резолюция, зададена от арбитъра и подадена на входа на съответния инициатор, към който принадлежи този сигнал.

Сигналите за грешка включват сигналите PERR# и SERR#.

PERR# s/t/s – грешка в паритета, генерирана от агента, който е открил грешката в паритета. Минималната продължителност на този сигнал е един тактов цикъл за всяка фаза на данните.

Групата сигнали на системата се състои от сигналите CLK и RST#.

CLK in - тактови импулси, които контролират формирането на всички сигнали на PCI шината, с изключение на сигналите за нулиране и прекъсване, по нарастващия фронт.

RST# in - нулиране, настройва регистрите в първоначалното им състояние.

Като незадължителни сигнали разглеждайте само сигналите за прекъсване.

INTA# o/d – прекъсване A. Сигнал за искане за прекъсване за еднофункционални агенти.

INTB# - INTD# o/d – заявки за прекъсване само за многофункционални агенти на PCI шина.

Запис на паметта

Многократно четене на паметта

Четене на линейна памет

Запишете в паметта и нулирайте

Конфигурацията се чете от конфигурационната област на необходимия агент. Агент е избран, ако неговият IDSEL е активен.

Писането на конфигурация се състои в прехвърляне на данни към конфигурационната памет, избрана от IDSEL сигнала на съответния агент.

Множество четения на паметта се използват от главния за често прехвърляне на големи количества данни, ако има софтуерно достъпен буфер за данни (кеш).

Линейно четене на паметта е команда, подобна на командата четене на паметта, с изключение на това, че главният изпълнява повече от две 32-битови фази на данни. Тази команда се използва при често прехвърляне на големи количества данни.

Записите в паметта и нулите позволяват оптимално използване на паметта, гарантирайки минимум прехвърляния за запълване на един кеш и изискват размера на кеша, посочен в конфигурационния регистър.

Пакетирането се извършва от шлюз между процесора и PCI шината, тъй като в момента процесорът изпълнява само една фаза на данни. Ако устройство с една фаза на данни е свързано към PCI шината, то (в случай на многофазен трансфер) след първата фаза то прекъсва достъпа до себе си. За правилна работа на устройството всички I/O достъпи се появяват на PCI шината веднага щом процесорът ги генерира.

Забележка: 0 – C/BE# сигналът е активен,

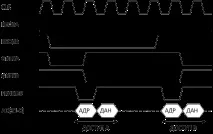

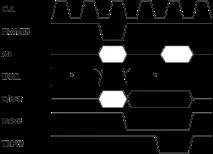

Контролът на трансфера на данни се извършва с помощта на три сигнала: FRAME#, IRDY#, TRDY#. Сигналът FRAME# се генерира от главния и указва началото и края на събитие в шината. Ако сигналите FRAME# и IRDY# са изключени (високи нива), тогава интерфейсът е неактивен (в пасивно състояние).

На фиг. Фигура 5.2 е времева диаграма на четене, която, за да се опрости чертежа, показва две фази на трансфер на данни (TX) (DAN1 и DAN2) и един цикъл на изчакване (WAIT), зададен от главния, използвайки сигнала TRDY#.

Ориз. 5.2. Четене на времевата диаграма

Събитие в автобуса може да бъде прекратено от капитана или целта. Ако събитието е прекратено от главния, то премахва FRAME#, докато IRDY# е активен, информирайки целта за предстоящата фаза на окончателните данни. Тази последна фаза на данни възниква, когато сигналите IRDY# и TRDY# са активни. След това сигналът IRDY# се нулира и заедно със сигнала FRAME# придобива неактивно ниво, което означава състояние на празна шина.

За спиране на събитието в шината от целевата страна се използва сигналът STOP#, който трябва да е активен, докато FRAME# стане неактивен.

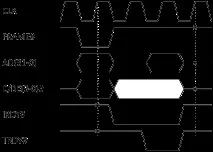

В случай, че никой подчинен не отговаря на главния, тогава ако сигналът DEVSEL# е изчистен, той завършва събитие в шината, което се нарича главен аборт, докато сигналите FRAME# и DEVSEL# се нулират. Времевата диаграма на запис на данни е показана на фиг. 5.3.

Записът започва със задаване на сигнала FRAME#. На фиг. Фигура 5.3 показва две фази на данни и един цикъл на заспиване, който се задава чрез премахване на сигнала IRDY# от главния.

Ориз. 5.3. Запис на времева диаграма

Ако има множество инициатори на PCI шината, се предоставя централизирана арбитражна процедура, която е възможна по време на предишния достъп (скрит арбитраж).

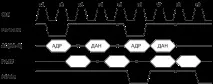

На фиг. Фигура 5.4 показва времето на арбитража.

Диаграмата илюстрира взаимодействието на два агента A и B на PCI шината. Първо агент А задава първата заявка REQ#A за управление на шината към арбитъра и получава достъп до нея с пристигането на сигнала GNT#A от арбитъра. От този момент агент А формира FRAME# и започва да прехвърля данни по шината. Сигналът REQ#A се държи от агент, който желае да продължи събитието в автобуса. Когато FRAME# на агент A е зададен, арбитърът приемапоискайте REQ#B на агент B и нулирайте сигнала GNT#A. С пристигането на този сигнал агент А прекратява трансфера на данни по шината и премахва сигналите FRAME# и IRDY# (освобождава интерфейса).

Ориз. 5.4. Времева диаграма на арбитража

Ако GNT#B сигналът на арбитъра е активен (нисък) и условието за освобождаване на интерфейса от агент A е изпълнено (сигналите FRAME# и IRDY# са пасивни), агент B поема контрола над интерфейса.Ако заявката REQ#B на агент B е премахната, това показва на арбитъра, че събитието в шината е завършено от агент B и арбитърът обслужва заявката на агент A. Арбитърът може да премахне GNT# на всеки агент B по всяко време, ако има по-висок приоритет Зададена е заявка REQ# на друг агент.

PCI шината прилага цикли на потвърждение на прекъсване. Времевата диаграма за цикъла на потвърждение на прекъсването е показана на фиг. 5.5.

Ориз. 5.5. Време за потвърждаване на прекъсване

Ориз. 5.6. Времева диаграма на паритета

Нека разгледаме някои изисквания към устройствата с PCI шина. Като формирачи (приемници) на шинни сигнали трябва да използвате елементи, които не консумират ток в статично състояние, а го консумират в моментите на превключване. Тези елементи включват CMOS (силициеви клетки с допълнително поле), които могат значително да намалят консумацията на енергия на устройството. За изграждане на интерфейсни схеми (контролери) можете да използвате програмируеми логически интегрални схеми (FPGA), произведени с помощта на CMOS технология, например Xilinx FPGA или местни аналози, произведени от Воронежския НИИЕТ.

Във външна платка, свързана чрез слот (конектор) към PCI шината, по-голямата част от тока се консумира от издърпващи резистори (2,7K при 5V),стабилизиране на стойностите на сигналите на PCI шината. В слота за PCI шина има два пина: PRSNT1# и PRSNT2#, кодовете на входовете на които се използват за индикация на външна платка в слота и определяне на консумацията на енергия от платката. Например код 00 показва, че има външна платка и нейната консумация на енергия е максимум 7,5 W. По този начин външната платка трябва да показва максималната консумация на енергия. Слотовете са свързани към четири захранващи шини: 5V, 3.3V, 12V и -12V. Максималната консумация на енергия на всяка външна платка е 25W. Драйверите трябва да имат ниско ниво на изходен ток (без резистор) - 3 mA или 6 mA с резистор. Максималният изходен капацитет на компонента е 10 pF, а максималната дължина на следата от конектора на платката до елемента е не повече от 3,8 см. Сигналът на шината трябва да бъде ограничен до едно натоварване.

В заключение на тази тема ще разгледаме връзката на два регистъра P1 и P2, достъпни за запис и четене, към PCI шината (фиг. 5.7), като за опростяване на фигурата не се разглежда конфигурационната памет.

Ориз. 5.7. Структурна схема на изпълнителя на PCI шина

Ако не е възможно да се изпълни това условие, образуването на TRDY# трябва да се забави с един цикъл, т.е. влиза в цикъл на изчакване в работата на инициатора. Схемата не използва приемо-предавател на данни, който въвежда забавяне, както например в контролерите на шината ISA, вместо него се използват два формовчика с три състояния (FOR). В допълнение, когато чете данни, веригата за контрол на четността (CK) генерира изходен сигнал PAR#, а когато записва данни, сравнява входния сигнал PAR# с резултата от паритета на получените данни. Ако бъде открита грешка, се задава сигналът PERR#.

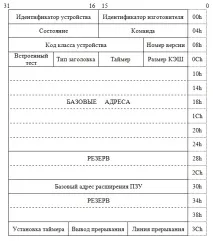

В заглавния формат първите 16 байта са стандартни за PCI устройства, а следващите 48 байта могат да бъдатразлични разположения в зависимост от основните функции на тези устройства. Конкретна (произволна) информация за устройствата се записва в байтове конфигурационна памет в диапазона 64-256.

Ориз. 5.8. Формат на заглавката на конфигурацията

Идентификаторите на устройството и производителя определят съответно типа (номера) на устройството и неговия производител.

Кодовете на класове на устройства съдържат кодове на базов клас (старши байтове при отместване 0Bh), които дефинират класове на устройства на голямо ниво.

Разграничават се следните класове устройства и техните кодове: контролери за масово съхранение (01h), мрежови контролери (02h), адаптери за дисплей (03h), мултимедийни устройства (04h), контролери за памет (05h) и мостове (06h).

Средният байт (отместване 0Ah) на кода на класа съдържа кода на подкласа на устройството. Например за базов клас 01h, SCSI контролерът е подклас 00h, IDE контролерът е подклас 01h, контролерът на флопи диск е подклас 02h и т.н.

Най-малко значимият бит (отместване 09h) дефинира интерфейса за програмиране на ниво регистър. Обикновено този байт е 00h.

Базовият клас мостове (код 06h) има следните подкласове: основен мост (00h), ISA мост (01h), EISA мост (02h), MC мост (03h), PCI-PCI мост (04h) и др.

Номерът на версията е даден от производителя и може да се счита за разширение на номера на устройството. Вграденият тест, ако има такъв, се управлява от съдържанието на съответния регистър на формата на заглавката на конфигурацията. В допълнение, резултатите от теста (битове за завършване) се отбелязват в този регистър.

Таймер, включен в заглавката, отчита броя на циклите на PCI шината и определя времето, което е позволено на главния да освободи шината, ако има други заявки за улавяне на шината.

Размерът на кеша се дава от броя на 32-битовитеданни и е необходим за определяне на границата на предаване на пакети данни.

Регистърът за настройка на таймера (2 байта) е предназначен да зададе продължителността на пакетния период и честотата на достъп до PCI шината. Изходният регистър за прекъсване (8 бита) определя кой сигнал за прекъсване използва устройството, например стойност 1 съответства на сигнала INTA#, стойност 2 на сигнала INTB# и т.н. Регистърът на линията за прекъсване съхранява информация за свързването на щифта за прекъсване на устройството към входа на контролера за прекъсване на системата, т.е. съобщава се номерът на заявката на контролера за прекъсване на системата.

Времевата диаграма за четене на конфигурационната памет е показана на фиг. 5.9.

Ориз. 5.9. Четене на конфигурационната памет

Достъп от тип 1 (достъп до устройство на различна шина) се определя от битове D1 D0, зададени на 01. Този достъп използва битове D23-D16 в регистъра PAR, за да изберете една от 128-те шини в системата.

Фигура 5.10. Схема за транслиране на RAK съдържание към AD шината

Конекторът на PCI шината е показан на фиг. 5.11, в който за по-лесно поставяне номерата на щифтовете са представени в две колони.