Синхронен трансфер на данни чрез SPI интерфейс

SPI интерфейсът (Serial Peripheral Interface) се използва за обмен на данни с периферни устройства. Такива устройства могат да бъдат прости регистри за смяна или модули за буквено-цифров дисплей, както и сложни микропроцесорни системи или системи за регистриране на данни. Много производители предлагат широка гама от SPI устройства.

В случай на обмен на данни през SPI интерфейса, микроконтролерът работи в режим на главно устройство (Master), взаимодействайки с едно или повече подчинени устройства (Slave). Схемата за пренос на данни чрез SPI интерфейса на микроконтролерите AVR / PIC е показана на фиг. 7.6 (MSB е най-значимият бит, а LSB е най-младшият бит от предавания байт).

Ориз. 7.6. Схема за пренос на данни през SPI интерфейса на AVR микроконтролери

Главното устройство поема активната част от комуникацията, предизвиквайки трансфера и контролирайки процеса. Самият роб не може да бъде активен. Той получава и предава данни само когато е активиран от главния на линията /SS. Главното устройство също генерира часовник за предаване по изходната линия SCK. За подчинения блок щифтът SCK е входът, през който той получава часовникови сигнали от главното устройство.

Ако подчиненото устройство се активира от главното чрез линията /SS, тогава започва обменът на данни: главният записва байта, който трябва да бъде прехвърлен в неговия регистър за изместване на данни (за микроконтролери AVR - регистър SPDR, за микроконтролери PIC - регистър SSPBUF). С всеки генериран тактов импулс главният премества един бит данни към изхода MOSI/SDO, а подчиненият едновременно прехвърля един бит в обратна посока към входа MISO/SDI на главния модул. Така по време на SPI цикъл от осем тактаимпулси, Master и Slave обменят байт данни.

В края на прехвърлянето на данни съответният флаг за искане за прекъсване се задава в регистъра за състояние на SPI интерфейса. Този флаг показва края на трансфер и предизвиква искане за прекъсване, след като битът за разрешаване на SPI прекъсване е зададен в контролния регистър на SPI. В режим "Master" текущият трансфер на данни може да бъде преждевременно завършен чрез подаване на лог сигнал към линията /SS. 1.

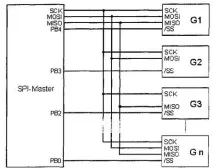

Няколко подчинени устройства могат да бъдат свързани към SPI интерфейса на главното устройство (пример за AVR микроконтролери е показан на фиг. 7.7), но само едно от тях ще бъде активно, на /SS входа на което ще се приложи нивото на журнал. 0. MISO изходите на неизползваните подчинени устройства са в състояние на високо съпротивление и не влияят на процеса на пренос на данни.

В примера на фиг. 7.7 устройство G2, от гледна точка на главното устройство, е само предавателно устройство (например DAC със SPI интерфейс), а устройство G3 е само приемащо устройство.

Ориз. 7.7. Свързване на множество подчинени устройства към едно главно чрез SPI (за AVR)

В микроконтролерите AVR щифтовете на порт B се използват като SPI линии (Таблица 7.2). В PIC микроконтролерите, за сериен синхронен трансфер на данни, MSSP портът работи в интерфейсен режим SPI или I2C. SPI линиите съответстват на щифтовете A и C на порта (Таблица 7.2).

Таблица 7.2. Изводи на портове за SPI интерфейсни линии

| Линия | AVR микроконтролери | PIC микроконтролери |

| /SS | Изпускателен порт 4 B | Зависи от модела (например бит 5 на порт A) |

| MOSI (SDO) | Бит 5 порт B | Бит 5 порт C |

| MISO (SDI) | Ранг 6Порт Б | Изпускане 4 порт C |

| SCK | Бит 7 порт B | Изпускателен порт 3 C |

SPI управление и регистри за състояние в AVR микроконтролери

| ШПИОН | SPE | ДОРД | MSTR | CPOL | CPHA | SPR1 | SPR0 |

Ориз. 7.8. SPCR контролен регистър на AVR микроконтролери

В края на прехвърлянето на данни през SPI интерфейса хардуерът задава SPIF бита (флаг за прекъсване от SPI интерфейса) в регистъра на състоянието на SPCR. Този флаг показва завършването на прехвърлянето и води до искане за прекъсване веднага щом битът SPIE бъде зададен в контролния регистър SPCR и общият флаг за разрешаване на прекъсване I е зададен в регистъра на състоянието SREG.

Битът SPE разрешава SPI интерфейса (log. 1) или го забранява (log. 0). След получаване на сигнала за нулиране, този бит приема стойността на дневника. 0 и по този начин SPI системата е деактивирана.

Ако битът DORD съдържа лог. 0, най-значимият бит от байта данни ще бъде предаден първи. При DORD = 1 най-младшият бит се предава първи.

Когато битът MSTR съдържа дневник. 0, тогава SPI системата се дефинира като подчинена (Slave), а при MSTR = 1 ще се дефинира като главна (Master). Когато линията /SS в режим Master е конфигурирана като вход, битът MSTR се нулира на дневник, когато нивото на сигнала на щифта /SS е ниско. 0 и по този начин SPI интерфейсът се определя като Slave. В този случай SPIF флагът е зададен в регистъра на състоянието.

Когато битът CPOL съдържа дневник. 0, SCK изходът е неактивен нисък. Ако CPOL = 1, тогава SCK е неактивен висок. С помощта на този бит, както и на бита SRHA (избор на фаза на часовника), се задава един от четирите режима.пренос на данни през интерфейса SPI (Таблица 7.3).

Битовете SPR1 и SPR0, когато SPI интерфейсът е в главен режим, се използват за избор на тактова честота за линията SCK. Ако SPI системата е конфигурирана като Slave, тогава тези битове нямат значение. Връзката между битовете SPR1, SPR0 и честотата на импулса в линията SCK е показана в таблица. 7.4.

Таблица 7.3. Режими на пренос на данни през SPI интерфейс в MK AVR

| CPOL | SRNA | Описание на режима |

| Главният поставя реда /SS в състояние на журнал. 0. За съответното подчинено устройство предаването започва при спадащия фронт на този сигнал. Неговият MISO изход преминава от висок към активен и MSB на байта в неговия SPDR регистър на данни се появява на изхода на MISO. Мастерът започва действителното прехвърляне на данни, като записва байта данни, който трябва да бъде прехвърлен в неговия SPDR регистър. След това най-значимият бит се появява на MOSI изхода на главния блок. По време на първата половина на първия тактов импулс, тактовата линия е все още в покой, за да се осигури стабилна настройка на съответния битов вход на данните. По нарастващия фронт на първия и всеки следващ тактов импулс се приемат битовете, разположени на входовете Master и Slave, а по спадащия фронт следващият бит се измества допълнително. След осмия тактов импулс прехвърлянето на данни е завършено, SPIF флаговете в регистрите за състояние на главния и подчинения блок са зададени и съдържанието на регистрите за изместване ще бъде прехвърлено към съответните приемащи буфери. MOSI изходът на главния се връща към празен ход (дневник 1), а MISO изходът на подчинения обикновено е най-значимият бит от байта, току-що получен от главния. Едновременно с нулирането на реда /SS към оригиналасъстояние (log. 1) Главният завършва прехвърлянето, подчиненият става неактивен и неговият MISO изход преминава в състояние с високо съпротивление | ||

| Подобно на случая, описан по-горе, с тази разлика, че състоянието на покой на часовниковата линия е зададено тук в log. 1, битовете данни се получават при първия и всеки следващ тактов импулс и изместването се извършва при нарастващия фронт на сигнала | ||

| За да започне прехвърлянето на данни в този режим, Master, както и в първия случай, поставя реда /SS в състояние на журнал. 0. Блокът Slave е активиран и неговият MISO изход преминава от висок към активен. Логическото ниво на MISO не е дефинирано за този случай, но MISO обикновено е най-малкият бит от байта, прехвърлен по време на предишното предаване от подчиненото към главното. Действителното прехвърляне на данни на Master в този режим започва със запис на байта данни, който трябва да бъде прехвърлен в SPDR регистъра. За подчиненото устройство предаването започва при нарастващия фронт на тактовия сигнал. MSB на байтовете, които трябва да бъдат прехвърлени в главния и подчинения блок, се задават от нарастващия фронт на първия тактов импулс на MOSI изхода на главния блок (MISO изход на подчинения блок). По спадащия фронт на първия и всеки следващ тактов импулс те се прехвърлят към главния и подчинения вход, а по нарастващия фронт се измества следващият бит. След осмия тактов импулс прехвърлянето на данни е завършено, SPIF флаговете се задават в регистрите за състояние на интерфейсите Master и Slave и съдържанието на техните регистри за изместване се прехвърля към съответните приемащи буфери. MOSI изходът на главния се връща в своето състояние на неактивност (дневник 1), оставяйки MISO изхода на подчинения с най-малкия бит от байта, току-що изпратен на главния. Едновременно с връщането къмпървоначално състояние на линията /SS (log. 1) Главният завършва прехвърлянето като цяло, подчиненият става неактивен и неговият MISO изход преминава в състояние на високо съпротивление. | ||

| Подобно на случая, описан по-горе, с тази разлика, че състоянието на покой на часовниковата линия тук е дневник. 1, а битовете данни се изместват по спадащия фронт на първия и всеки следващ тактов импулс и се получават по нарастващия фронт |

Таблица 7.4. Честотата на импулсите в SCK линията зависи от битовете SPR1, SPR0

| SPR1 | SPR0 | Честота на импулса в линията SCK |

| Системен часовник / 4 | ||

| Системен часовник /16 | ||

| Системен часовник / 64 | ||

| Системен часовник /128 |

бит 6 - WCOL флаг - се задава, когато по време на прехвърляне на данни през SPI интерфейса се направи опит за запис в регистъра на SPI данни, което води до унищожаване на току-що прехвърления байт данни. Поради тази причина текущият трансфер на данни се довежда до завършване и не се записва нов байт в регистъра за изместване на SPI интерфейса. WCOL флагът трябва да бъде нулиран ръчно от потребителя чрез четене на регистъра на състоянието и след това достъп до SPI регистъра на данните;

Бит 7 - SPIF флаг - Показва завършването на прехвърлянето и предизвиква заявка за прекъсване, веднага щом битът SPIE е зададен в контролния регистър SPCR и битът I е зададен в регистъра на състоянието SREG.Когато линията /SS е конфигурирана като вход в режим Master, флагът SPIF също ще бъде зададен на щифта на линията /SS, когато сигналът е нисък. SPIF флагът се изчиства автоматично от хардуера при изпълнение на рутинна услуга за прекъсване от SPI интерфейса.Алтернативно, нулирането може да се извърши ръчно чрез четене на регистъра за състояние на SPSR и след това достъп до регистъра на данните на SPI интерфейса.