Готово 3

Лаборатория #3

Регистри и броячи.

Функциите на цифровите устройства, разбира се, не се ограничават до изпълнението на различни FAL. Бихме искали да използваме цифрови устройства за обработка на информация, изчисления. Но за да реализираме тези възможности, ни липсва елемент на паметта, който да съхранява междинни резултати. В крайна сметка е невъзможно да се направи калкулатор, ако няма начин да се запазят въведените числа и резултатът от изчислението.

Паметта е един от най-важните елементи на цифровите устройства. За да не допускате грешки при проектирането на цифрови устройства, е необходимо да разберете мястото на този възел, неговата идея и свързаните с него инструменти на езика Verilog.

Първият елемент на паметта, който ще разгледаме, ерезето(на английскиlatch)

Резето е в основата на всички елементи на паметта. Състои се от два елемента NAND (или два елемента NOR, в зависимост от основата, избрана при проектирането), свързани по следната схема:

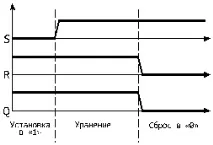

Резето има два входа и два изхода. Входовете са сигналите "reset" и "set to one" или на английски "reset" и "set". В зависимост от елементите, които съставят резето, полярността на входните сигнали ще се промени. В основата на NAND нулирането и настройката се случват, когато R или S сигналите са на нула, съответно, така че те се наричат "ненулирани" и "ненастроени", за да отразят този факт. Резултатът от ключалката е битът данни, който съхранява. Двата изхода се различават по полярност - единият от тях инвертира запаметения бит. По-долу има таблица с всички възможни комбинации от входни сигнали и времева диаграма на резето.

Нека опишем резето във Verilog въз основа на неговата структура, която ниеразгледани по-горе. Имаме нужда от два входа, два изхода и два NAND елемента, които описваме с помощта на AND (& оператор) и NOT (оператор