Какво е JTAG

Веднъж и аз се уплаших от мистериозното съкращение - JTAG. По всякакъв начин отлагах момента на близкото запознанство с него, но сега той дойде. В тази статия искам да кажа и да покажа, че не всичко е толкова просто - на мнозина изглежда, че JTAG е вид "дантела" и това е всичко. JTAG трябва да се разбира като вид технология, която преследва определени цели. Така че да започнем по ред.

Тест за JTAG Boudaty-Scan (BST)

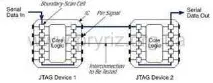

През 1985 г. е създадена специална група от водещи производители на електроника - JTAG (Joint Test Action Group). За да разреши проблемите с тестването, JTAG популяризира спецификацията IEEE Std 1149.1-1990 (IEEE Standard Test Access Port and Boundary-Scan Architecture) като индустриален стандарт. Включването на BST архитектурата в съвременните чипове осигурява достъп до щифтовете на чипа (по-точно до специални I/O блокове) с помощта на 4-жилен JTAG сериен интерфейс. Тази архитектура позволява не само да се контролира състоянието им, но и да се управляват. По този начин могат да се откажат от обемисти сонди с физически контакт.

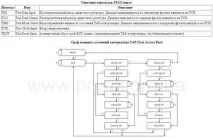

Както може да се види от графиката, TAP контролерът ще превключи към първоначално състояние RESET от всяко друго за не повече от 5 TCK импулса при TMS=1. В този случай цялата верига BST ще бъде нулирана и стойността по подразбиране ще бъде записана в регистъра на инструкциите (обикновено инструкцията IDCODE, но може да бъде и друга, например SAMPLE. За да се избегне това нулиране, TAP контролерът трябва да премине през безопасно състояние IDLE, в което се записват всички работни настройки. Веригата BST съдържа цял набор от регистри за преместване. При преминаване през десния клон на графиката, регистър на инструкции с дължина 3 битове, заредената инструкция определя един от наличните регистри на данни при преминаване през левия клон и действията с тяхв определени състояния на TAP контролера. От тези регистри обикновено има най-малко външен регистър за достъп до щифта на чипа и еднобитов байпасен регистър. Тъй като всички преместващи регистри във верига от JTAG устройства се добавят в един дълъг, байпасният регистър позволява да се намали тази дължина, представяйки байпасираните устройства само с един бит. За това се използва инструкцията BYPASS. Тъй като въвеждането на BYPASS инструкция отменя ефекта на предварително заредена инструкция, за съжаление не е възможно да се запази състоянието на I/O блокове, зададени от инструкции като EXTEST и INTEST. Изключение прави инструкцията CLAMP, след която можете да използвате регистъра за байпас. Но тази инструкция практически не съществува. В регистъра за достъп за всеки входно-изходен блок на FPGA по правило се разпределят три последователни бита: вход (I), изход (O) и изходен инхибит (T). Редът на битовия изход на TDO е различен за FPGA от различни компании. Например за Xilinx - (T,O,I), а за Altera - (I,T,O). В състояние CAPTURE текущото състояние се записва в избрания регистър за смяна. Между другото, за регистъра на инструкциите това обикновено е кодът на инструкция SAMPLE, а за регистъра на байпаса това е логическа единица. В състояние UPDATE, данните в регистъра за изместване се записват в съответния регистър за съхранение. По този начин инструкцията SAMPLE не само чете текущото състояние на външните изводи, но също така записва контролни данни в регистъра за съхранение. Следователно, за да се избегне извеждането на произволна информация, тя се използва преди зареждане на инструкции като EXTEST или INTEST. Когато инструкцията EXTEST е заредена, изходите на регистъра за съхранение определят състоянието на изходите на чипа, т.е. контролира изхода и третото му състояние. По този начин могат да бъдат тествани външни връзки. Инструкцията INTEST, напротив, замества сигналапоставен вътре в чипа и служи за тестване на самия чип. Често една единствена инструкция EXTEST не се използва, като се използва входният (I) бит за въвеждане на чипа, както в инструкцията INTEST. Инструкцията IDCODE свързва вграден 32-битов регистър с идентификатори на производителя, модела и версията на устройството.

Наборът от инструкции се определя от производителя. Присъстват минимум SAMPLE и BYPASS и EXTEST. Останалите инструкции не са задължителни. Както вече споменахме, за FPGA може да има специални инструкции за конфигуриране, а за процесори - четене на резултата от вътрешен тест. Производителите на чипове предоставят специфична информация за внедряване на BST за всеки тип техен продукт под формата на файл с език за описание на гранично сканиране (BSDL). Малко повече информация за този формат можете да намерите на http://www.asset-intertech.com. JTAG портът може да бъде достъпен с помощта на кабел ByteBlaster чрез свързване на тестваната система към паралелния порт на компютъра. В тестваната система се препоръчва да се инсталират издърпващи резистори (PullUp's) и керамичен кондензатор на захранването близо до свързващия конектор (което успешно използвам в моя JTAG интерфейс на чипа 74HC244, като поставям керамичен кондензатор на захранването му, като се има предвид, че понякога трябва да вземете захранване от приемника ...... ..). За стабилна работа е желателно да се буферира TDO изхода. Например чрез два инвертора от типа K561LN2.

Радиокомпоненти, устройства, дискове, литература по пощата.